# ST24C04, ST25C04 ST24W04, ST25W04

# 4 Kbit Serial I<sup>2</sup>C Bus EEPROM with User-Defined Block Write Protection

#### **NOT FOR NEW DESIGN**

- 1 MILLION ERASE/WRITE CYCLES with 40 YEARS DATA RETENTION

- SINGLE SUPPLY VOLTAGE:

- 3V to 5.5V for ST24x04 versions

- 2.5V to 5.5V for ST25x04 versions

- HARDWARE WRITE CONTROL VERSIONS: ST24W04 and ST25W04

- PROGRAMMABLE WRITE PROTECTION

- TWO WIRE SERIAL INTERFACE, FULLY I<sup>2</sup>C BUS COMPATIBLE

- BYTE and MULTIBYTE WRITE (up to 4 BYTES)

- PAGE WRITE (up to 8 BYTES)

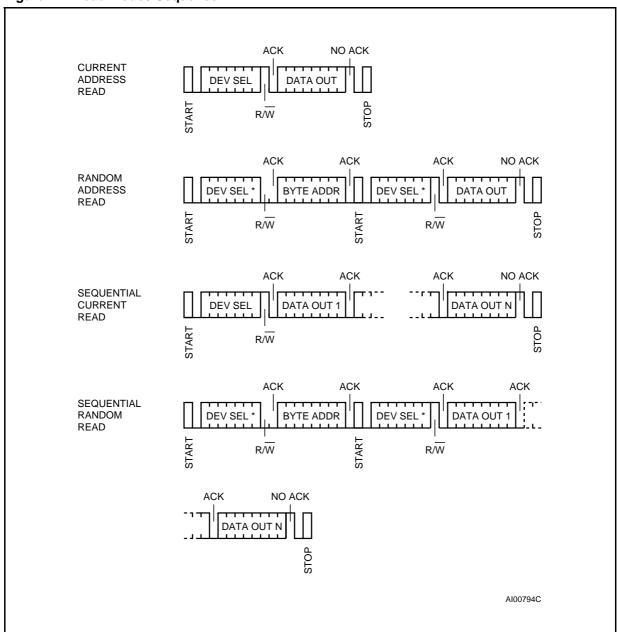

- BYTE, RANDOM and SEQUENTIAL READ MODES

- SELF TIMED PROGRAMMING CYCLE

- AUTOMATIC ADDRESS INCREMENTING

- ENHANCED ESD/LATCH UP PERFORMANCES

### **DESCRIPTION**

This specification covers a range of 4 Kbits I<sup>2</sup>C bus EEPROM products, the ST24/25C04 and the ST24/25W04. In the text, products are referred to as ST24/25x04, where "x" is: "C" for Standard version and "W" for hardware Write Control version.

**Table 1. Signal Names**

| PRE   | Write Protect Enable                     |

|-------|------------------------------------------|

| E1-E2 | Chip Enable Inputs                       |

| SDA   | Serial Data Address Input/Output         |

| SCL   | Serial Clock                             |

| MODE  | Multibyte/Page Write Mode<br>(C version) |

| WC    | Write Control (W version)                |

| Vcc   | Supply Voltage                           |

| Vss   | Ground                                   |

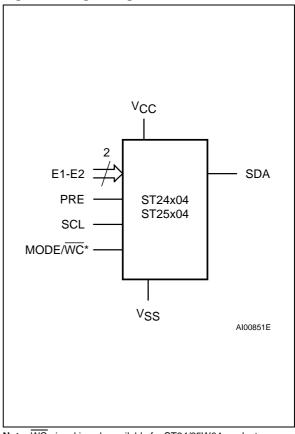

Figure 1. Logic Diagram

Note: WC signal is only available for ST24/25W04 products.

December 2002 1/16

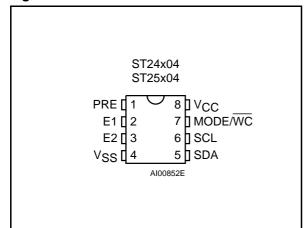

Figure 2A. DIP Pin Connections

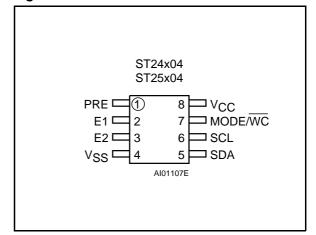

Figure 2B. SO Pin Connections

Table 2. Absolute Maximum Ratings (1)

| Symbol            | Parameter                                                                | Value       | Unit |

|-------------------|--------------------------------------------------------------------------|-------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature                                            | -40 to 125  | °C   |

| T <sub>STG</sub>  | Storage Temperature                                                      | -65 to 150  | °C   |

| T <sub>LEAD</sub> | Lead Temperature, Soldering (SO8 package) 40 sec (PSDIP8 package) 10 sec | 215<br>260  | °C   |

| V <sub>IO</sub>   | Input or Output Voltages                                                 | -0.6 to 6.5 | V    |

| Vcc               | Supply Voltage                                                           | -0.3 to 6.5 | V    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human Body model) (2)                   | 4000        | V    |

| V ESD             | Electrostatic Discharge Voltage (Machine model) (3)                      | 500         | V    |

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents

- relevant quality documents. 2. MIL-STD-883C, 3015.7 (100pF, 1500  $\Omega$ ).

- 3. EIAJ IC-121 (Condition C) (200pF, 0 Ω).

# **DESCRIPTION** (cont'd)

The ST24/25x04 are 4 Kbit electrically erasable programmable memories (EEPROM), organized as 2 blocks of 256 x8 bits. They are manufactured in STMicroelectronics's Hi-Endurance Advanced CMOS technology which guarantees an endurance of one million erase/write cycles with a data retention of 40 years.

Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

The memories are compatible with the I<sup>2</sup>C standard, two wire serial interface which uses a bi-directional data bus and serial clock. The memories

carry a built-in 4 bit, unique device identification code (1010) corresponding to the I<sup>2</sup>C bus definition. This is used together with 2 chip enable inputs (E2, E1) so that up to 4 x 4K devices may be attached to the I<sup>2</sup>C bus and selected individually. The memories behave as a slave device in the I<sup>2</sup>C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010), plus one read/write bit and terminated by an acknowledge bit.

**Table 3. Device Select Code**

|               | Device Code |    |    |    | Chip I | Enable | Block<br>Select | R₩ |

|---------------|-------------|----|----|----|--------|--------|-----------------|----|

| Bit           | b7          | b6 | b5 | b4 | b3     | b2     | b1              | b0 |

| Device Select | 1           | 0  | 1  | 0  | E2     | E1     | A8              | RW |

Note: The MSB b7 is sent first.

Table 4. Operating Modes (1)

| Mode                 | RW bit | MODE            | Bytes    | Initial Sequence                                      |

|----------------------|--------|-----------------|----------|-------------------------------------------------------|

| Current Address Read | '1'    | Х               | 1        | START, Device Select, RW = '1'                        |

| Random Address Read  | '0'    | Х               | 1        | START, Device Select, $R\overline{W}$ = '0', Address, |

| Nandom Address Nead  | '1'    | ^               | 1        | reSTART, Device Select, RW = '1'                      |

| Sequential Read      | '1'    | Х               | 1 to 512 | Similar to Current or Random Mode                     |

| Byte Write           | '0'    | Х               | 1        | START, Device Select, RW = '0'                        |

| Multibyte Write (2)  | '0'    | V <sub>IH</sub> | 4        | START, Device Select, $R\overline{W}$ = '0'           |

| Page Write           | '0'    | V <sub>IL</sub> | 8        | START, Device Select, RW = '0'                        |

Notes: 1.  $X = V_{IH}$  or  $V_{IL}$

2. Multibyte Write not available in ST24/25W04 versions.

When writing data to the memory it responds to the 8 bits received by asserting an acknowledge bit during the 9th bit time. When data is read by the bus master, it acknowledges the receipt of the data bytes in the same way. Data transfers are terminated with a STOP condition.

Power On Reset:  $V_{CC}$  lock out write protect. In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is implemented. Until the  $V_{CC}$  voltage has reached the POR threshold value, the internal reset is active, all operations are disabled and the device will not respond to any command. In the same way, when  $V_{CC}$  drops down from the operating voltage to below the POR threshold value, all operations are disabled and the device will not respond to any command. A stable  $V_{CC}$  must be applied before applying any logic signal.

#### **SIGNAL DESCRIPTIONS**

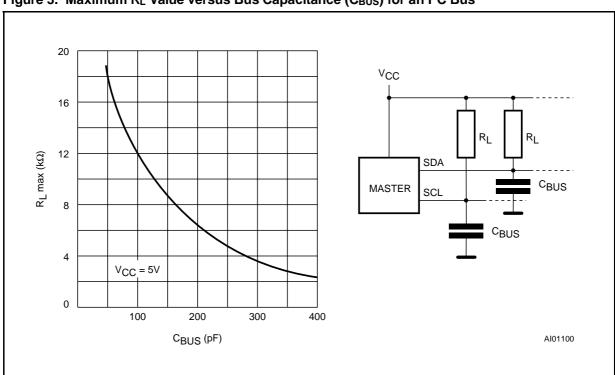

**Serial Clock (SCL).** The SCL input pin is used to synchronize all data in and out of the memory. A resistor can be connected from the SCL line to  $V_{CC}$  to act as a pull up (see Figure 3).

**Serial Data (SDA).** The SDA pin is bi-directional and is used to transfer data in or out of the memory. It is an open drain output that may be wire-OR'ed

with other open drain or open collector signals on the bus. A resistor must be connected from the SDA bus line to  $V_{CC}$  to act as pull up (see Figure 3).

Chip Enable (E1 - E2). These chip enable inputs are used to set the 2 least significant bits (b2, b3) of the 7 bit device select code. These inputs may be driven dynamically or tied to  $V_{CC}$  or  $V_{SS}$  to establish the device select code.

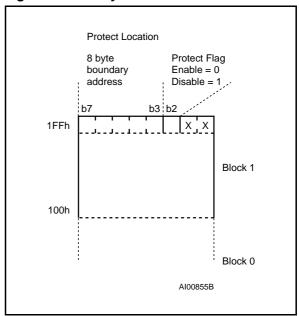

**Protect Enable (PRE).** The PRE input pin, in addition to the status of the Block Address Pointer bit (b2, location 1FFh as in Figure 7), sets the PRE write protection active.

**Mode (MODE).** The MODE input is available on pin 7 (see also  $\overline{WC}$  feature) and may be driven dynamically. It must be at  $V_{IL}$  or  $V_{IH}$  for the Byte Write mode,  $V_{IH}$  for Multibyte Write mode or  $V_{IL}$  for Page Write mode. When unconnected, the MODE input is internally read as  $V_{IH}$  (Multibyte Write mode).

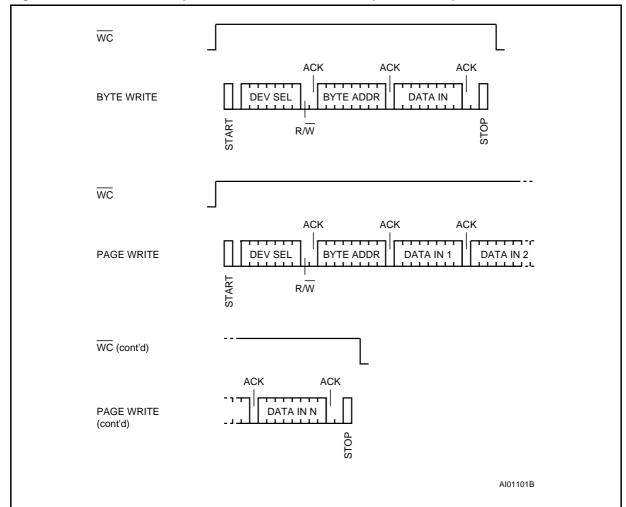

**Write Control (WC).** An hardware Write Control feature (WC) is offered only for ST24W04 and ST25W04 versions on pin 7. This feature is usefull to protect the contents of the memory from any erroneous erase/write cycle. The Write Control signal is used to enable (WC =  $V_{IH}$ ) or disable (WC =  $V_{IL}$ ) the internal write protection. When unconnected, the WC input is internally read as  $V_{IL}$  and the memory area is not write protected.

#### **SIGNAL DESCRIPTIONS** (cont'd)

The devices with this Write Control feature no longer support the Multibyte Write mode of operation, however all other write modes are fully supported.

Refer to the AN404 Application Note for more detailed information about Write Control feature.

#### **DEVICE OPERATION**

#### I<sup>2</sup>C Bus Background

The ST24/25x04 support the I<sup>2</sup>C protocol. This protocol defines any device that sends data onto the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master will always initiate a data transfer and will provide the serial clock for synchronisation. The ST24/25x04 are always slave devices in all communications.

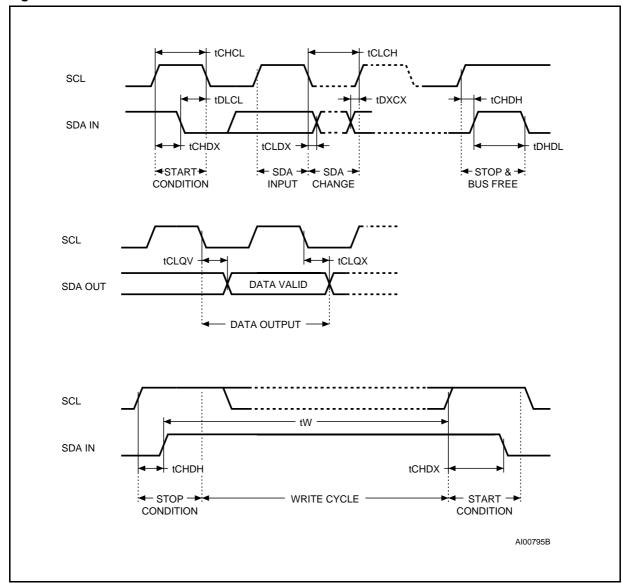

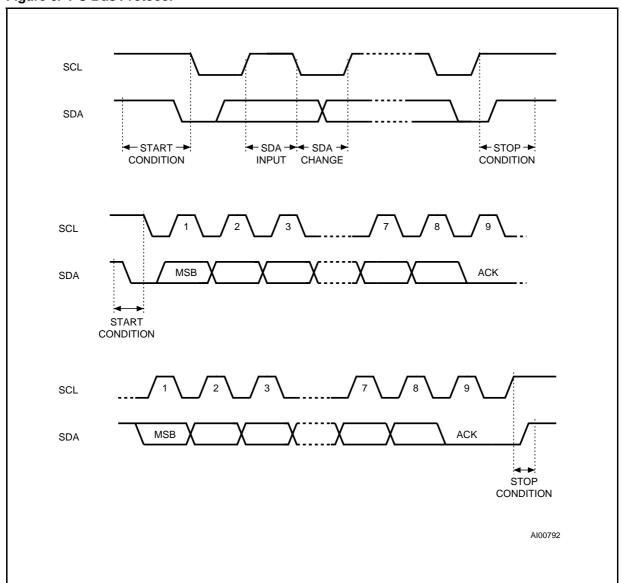

**Start Condition.** START is identified by a high to low transition of the SDA line while the clock SCL is stable in the high state. A START condition must precede any command for data transfer. Except during a programming cycle, the ST24/25x04 continuously monitor the SDA and SCL signals for a START condition and will not respond unless one is given.

**Stop Condition.** STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition terminates communication between the ST24/25x04 and the bus master. A STOP condition at the end of a Read command, after and only after a No Acknowledge, forces the standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.

Acknowledge Bit (ACK). An acknowledge signal is used to indicate a successfull data transfer. The bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data. During the 9th clock pulse period the receiver pulls the SDA bus low to acknowledge the receipt of the 8 bits of data.

**Data Input.** During data input the ST24/25x04 sample the SDA bus signal on the rising edge of the clock SCL. Note that for correct device operation the SDA signal must be stable during the clock low to high transition and the data must change ONLY when the SCL line is low.

**Memory Addressing.** To start communication between the bus master and the slave ST24/25x04, the master must initiate a START condition. Following this, the master sends onto the SDA bus line 8 bits (MSB first) corresponding to the device select code (7 bits) and a READ or WRITE bit.

Figure 3. Maximum R<sub>L</sub> Value versus Bus Capacitance (C<sub>BUS</sub>) for an I<sup>2</sup>C Bus

Table 5. Input Parameters <sup>(1)</sup> ( $T_A = 25$  °C, f = 100 kHz)

| Symbol           | Parameter                                         | Test Condition              | Min | Max | Unit |

|------------------|---------------------------------------------------|-----------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance (SDA)                           |                             |     | 8   | pF   |

| C <sub>IN</sub>  | Input Capacitance (other pins)                    |                             |     | 6   | pF   |

| Z <sub>WCL</sub> | WC Input Impedance (ST24/25W04)                   | $V_{IN} \leq 0.3 \; V_{CC}$ | 5   | 20  | kΩ   |

| Z <sub>WCH</sub> | WC Input Impedance (ST24/25W04)                   | $V_{IN} \ge 0.7 \ V_{CC}$   | 500 |     | kΩ   |

| t <sub>LP</sub>  | Low-pass filter input time constant (SDA and SCL) |                             |     | 100 | ns   |

Note: 1. Sampled only, not 100% tested.

Table 6. DC Characteristics ( $T_A = 0$  to  $70^{\circ}$ C, -20 to  $85^{\circ}$ C or -40 to  $85^{\circ}$ C;  $V_{CC} = 3V$  to 5.5V or 2.5V to 5.5V)

| Symbol           | Parameter                                                                  | Test Condition                                                    | Min                   | Max                 | Unit |

|------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------|---------------------|------|

| ILI              | Input Leakage Current                                                      | $0V \le V_{IN} \le V_{CC}$                                        |                       | ±2                  | μΑ   |

| I <sub>LO</sub>  | Output Leakage Current 0V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> SDA in Hi-Z |                                                                   |                       | ±2                  | μΑ   |

| Icc              | Supply Current (ST24 series)                                               | $V_{CC} = 5V$ , $f_C = 100$ kHz (Rise/Fall time < 10ns)           |                       | 2                   | mA   |

|                  | V <sub>IN</sub> = V <sub>SS</sub>                                          | $V_{CC} = 2.5V, f_C = 100kHz$                                     |                       | 1                   | mA   |

| I <sub>CC1</sub> | Supply Current (Standby)                                                   | $V_{IN} = V_{SS}$ or $V_{CC}$ ,<br>$V_{CC} = 5V$                  |                       | 100                 | μΑ   |

| ICC1             | (ST24 series)                                                              | $V_{IN} = V_{SS}$ or $V_{CC}$ ,<br>$V_{CC} = 5V$ , $f_C = 100kHz$ |                       | 300                 | μΑ   |

| I <sub>CC2</sub> | Supply Current (Standby)                                                   | $V_{IN} = V_{SS}$ or $V_{CC}$ ,<br>$V_{CC} = 2.5V$                |                       | 5                   | μΑ   |

| 1002             | (ST25 series)                                                              | $V_{IN} = V_{SS}$ or $V_{CC}$ , $V_{CC} = 2.5V$ , $f_C = 100kHz$  |                       | 50                  | μΑ   |

| V <sub>IL</sub>  | Input Low Voltage (SCL, SDA)                                               |                                                                   | -0.3                  | 0.3 V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | Input High Voltage (SCL, SDA)                                              |                                                                   | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 1 | V    |

| VIL              | Input Low Voltage (E1-E2, PRE, MODE, WC)                                   |                                                                   | -0.3                  | 0.5                 | ٧    |

| VIH              | Input High Voltage<br>(E1-E2, PRE, MODE, WC)                               |                                                                   | V <sub>CC</sub> - 0.5 | V <sub>CC</sub> + 1 | ٧    |

| V <sub>OL</sub>  | Output Low Voltage (ST24 series)                                           | $I_{OL} = 3mA$ , $V_{CC} = 5V$                                    |                       | 0.4                 | V    |

| V OL             | Output Low Voltage (ST25 series)                                           | $I_{OL} = 2.1 \text{mA}, V_{CC} = 2.5 \text{V}$                   |                       | 0.4                 | V    |

47/ 5/16

**Table 7. AC Characteristics**

$(T_A = 0 \text{ to } 70^{\circ}\text{C}, -20 \text{ to } 85^{\circ}\text{C} \text{ or } -40 \text{ to } 85^{\circ}\text{C}; \ V_{CC} = 3\text{V to } 5.5\text{V or } 2.5\text{V to } 5.5\text{V})$

| Symbol                        | Alt                 | Parameter                            | Min | Max | Unit |

|-------------------------------|---------------------|--------------------------------------|-----|-----|------|

| t <sub>CH1CH2</sub>           | t <sub>R</sub>      | Clock Rise Time                      |     | 1   | μs   |

| t <sub>CL1CL2</sub>           | t <sub>F</sub>      | Clock Fall Time                      |     | 300 | ns   |

| t <sub>DH1DH2</sub>           | t <sub>R</sub>      | Input Rise Time                      |     | 1   | μs   |

| t <sub>DL1DL1</sub>           | t <sub>F</sub>      | Input Fall Time                      |     | 300 | ns   |

| t <sub>CHDX</sub> (1)         | tsu:sta             | Clock High to Input Transition       | 4.7 |     | μs   |

| t <sub>CHCL</sub>             | t <sub>HIGH</sub>   | Clock Pulse Width High               | 4   |     | μs   |

| t <sub>DLCL</sub>             | t <sub>HD:STA</sub> | Input Low to Clock Low (START)       | 4   |     | μs   |

| t <sub>CLDX</sub>             | t <sub>HD:DAT</sub> | Clock Low to Input Transition        | 0   |     | μs   |

| tclch                         | t <sub>LOW</sub>    | Clock Pulse Width Low                | 4.7 |     | μs   |

| t <sub>DXCX</sub>             | t <sub>SU:DAT</sub> | Input Transition to Clock Transition | 250 |     | ns   |

| tchdh                         | t <sub>SU:STO</sub> | Clock High to Input High (STOP)      | 4.7 |     | μs   |

| t <sub>DHDL</sub>             | t <sub>BUF</sub>    | Input High to Input Low (Bus Free)   | 4.7 |     | μs   |

| t <sub>CLQV</sub> (2)         | t <sub>AA</sub>     | Clock Low to Next Data Out Valid     | 0.3 | 3.5 | μs   |

| t <sub>CLQX</sub>             | t <sub>DH</sub>     | Data Out Hold Time                   | 300 |     | ns   |

| f <sub>C</sub>                | f <sub>SCL</sub>    | Clock Frequency                      |     | 100 | kHz  |

| t <sub>W</sub> <sup>(3)</sup> | t <sub>WR</sub>     | Write Time                           |     | 10  | ms   |

Notes: 1. For a reSTART condition, or following a write cycle.

- 2. The minimum value delays the falling/rising edge of SDA away from SCL = 1 in order to avoid unwanted START and/or STOP

- In the Multibyte Write mode only, if accessed bytes are on two consecutive 8 bytes rows (6 address MSB are not constant) the maximum programming time is doubled to 20ms.

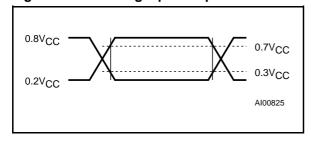

#### **AC MEASUREMENT CONDITIONS**

Input Rise and Fall Times  $\leq 50$ ns

Input Pulse Voltages 0.2V<sub>CC</sub> to 0.8V<sub>CC</sub>

Input and Output Timing Ref. Voltages 0.3V<sub>CC</sub> to 0.7V<sub>CC</sub>

Figure 4. ACTesting Input Output Waveforms

## **DEVICE OPERATION** (cont'd)

The 4 most significant bits of the device select code are the device type identifier, corresponding to the I<sup>2</sup>C bus definition. For these memories the 4 bits are fixed as 1010b. The following 2 bits identify the specific memory on the bus. They are matched to the chip enable signals E2, E1. Thus up to 4 x 4K memories can be connected on the same bus giving a memory capacity total of 16 Kbits. After a START condition any memory on the bus will identify the device code and compare the following 2 bits to its chip enable inputs E2, E1.

The 7th bit sent is the block number (one block = 256 bytes). The 8th bit sent is the read or write bit (RW), this bit is set to '1' for read and '0' for write operations. If a match is found, the corresponding memory will acknowledge the identification on the SDA bus during the 9th bit time.

Figure 5. AC Waveforms

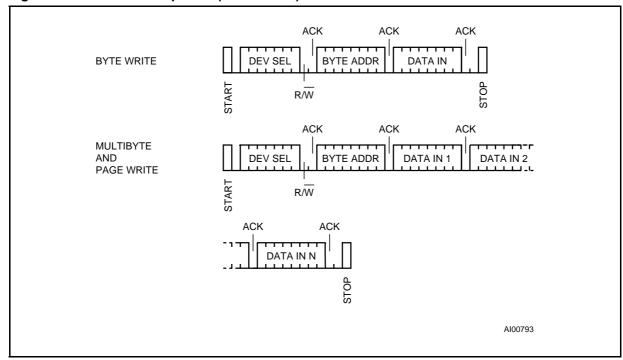

### **Write Operations**

The Multibyte Write mode (only available on the ST24/25C04 versions) is selected when the MODE pin is at  $V_{IH}$  and the Page Write mode when MODE pin is at  $V_{IL}$ . The MODE pin may be driven dynamically with CMOS input levels.

Following a START condition the master sends a device select code with the RW bit reset to '0'. The memory acknowledges this and waits for a byte address. The byte address of 8 bits provides access to one block of 256 bytes of the memory. After receipt of the byte address the device again responds with an acknowledge.

For the ST24/25W04 versions, any write command with  $\overline{WC}$  = 1 will not modify the memory content.

Byte Write. In the Byte Write mode the master sends one data byte, which is acknowledged by the memory. The master then terminates the transfer by generating a STOP condition. The Write mode is independant of the state of the MODE pin which could be left floating if only this mode was to be used. However it is not a recommended operating mode, as this pin has to be connected to either  $V_{IH}$  or  $V_{IL}$ , to minimize the stand-by current.

Figure 6. I<sup>2</sup>C Bus Protocol

**Multibyte Write.** For the Multibyte Write mode, the MODE pin must be at  $V_{IH}$ . The Multibyte Write mode can be started from any address in the memory. The master sends from one up to 4 bytes of data, which are each acknowledged by the memory. The transfer is terminated by the master generating a STOP condition. The duration of the write cycle is  $t_W = 10 \text{ms}$  maximum except when bytes are accessed on 2 rows (that is have different values for the 6 most significant address bits A7-A2), the programming time is then doubled to a maximum of 20 ms. Writing more than 4 bytes in the

Multibyte Write mode may modify data bytes in an adjacent row (one row is 8 bytes long). However, the Multibyte Write can properly write up to 8 consecutive bytes as soon as the first address of these 8 bytes is the first address of the row, the 7 following bytes being written in the 7 following bytes of this same row.

**Page Write.** For the Page Write mode, the MODE pin must be at  $V_{IL}$ . The Page Write mode allows up to 8 bytes to be written in a single write cycle, provided that they are all located in the same 'row' in the memory: that is the 5 most significant mem-

ory address bits (A7-A3) are the same inside one block. The master sends from one up to 8 bytes of data, which are each acknowledged by the memory. After each byte is transfered, the internal byte address counter (3 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition. Care must be taken to avoid address counter 'roll-over' which could result in data being overwritten. Note that, for any write mode, the generation by the master of the STOP condition starts the internal memory program cycle. All inputs are disabled until the completion of this cycle and the memory will not respond to any request.

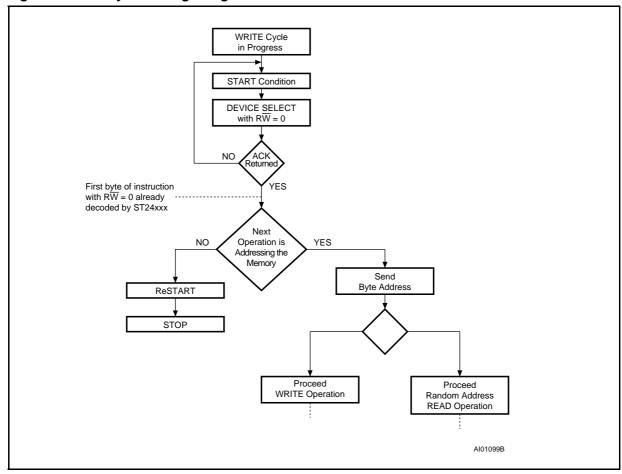

Minimizing System Delays by Polling On ACK. During the internal write cycle, the memory disconnects itself from the bus in order to copy the data from the internal latches to the memory cells. The maximum value of the write time (tw) is given in the AC Characteristics table, since the typical time is shorter, the time seen by the system may be reduced by an ACK polling sequence issued by the master.

Figure 7. Memory Protection

Figure 8. Write Cycle Polling using ACK

Figure 9. Write Modes Sequence (ST24/25C04)

#### **DEVICE OPERATION** (cont'd)

The sequence is as follows:

- Initial condition: a Write is in progress (see Figure 8).

- Step 1: the Master issues a START condition followed by a Device Select byte (1st byte of the new instruction).

- Step 2: if the memory is busy with the internal write cycle, no ACK will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it will respond with an ACK, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction was already sent during Step 1).

Write Protection. Data in the upper block of 256 bytes of the memory may be write protected. The memory is write protected between a boundary address and the top of memory (address 1FFh) when the PRE input pin is taken high and when the Protect Flag (bit b2 in location 1FFh) is set to '0'. The boundary address is user defined by writing it in the Block Address Pointer. The Block Address Pointer is an 8 bit EEPROM register located at the address 1FFh. It is composed by 5 MSBs Address Pointer, which defines the bottom boundary address, and 3 LSBs which must be programmed at

'0'. This Address Pointer can therefore address a boundary in steps of 8 bytes.

The sequence to use the Write Protected feature is:

- write the data to be protected into the top of the memory, up to, but not including, location 1FFh;

- set the protection by writing the correct bottom boundary address in the Address Pointer (5 MSBs of location 1FFh) with bit b2 (Protect flag) set to '0'. Note that for a correct fonctionality of the memory, all the 3 LSBs of the Block Address Pointer must also be programmed at '0'.

The area will now be protected when the PRE input pin is taken High. While the PRE input pin is read at '0' by the memory, the location 1FFh can be used as a normal EEPROM byte.

Caution: Special attention must be used when using the protect mode together with the Multibyte Write mode (MODE input pin High). If the Multibyte Write starts at the location right below the first byte of the Write Protected area, then the instruction will write over the first 3 bytes of the Write Protected area. The area protected is therefore smaller than the content defined in the location 1FFh, by 3 bytes. This does not apply to the Page Write mode as the address counter 'roll-over' and thus cannot go above the 8 bytes lower boundary of the protected area.

Figure 10. Write Modes Sequence with Write Control = 1 (ST24/25W04)

#### **Read Operations**

Read operations are independent of the state of the MODE pin. On delivery, the memory content is set at all "1's" (or FFh).

Current Address Read. The memory has an internal byte address counter. Each time a byte is read, this counter is incremented. For the Current Address Read mode, following a START condition, the master sends a memory address with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed by the internal byte address counter. This counter is then incremented. The master does NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

Random Address Read. A dummy write is performed to load the address into the address counter, see Figure 11. This is followed by another START condition from the master and the byte address is repeated with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed. The master have to NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

**Sequential Read.** This mode can be initiated with either a Current Address Read or a Random Address Read. However, in this case the master DOES acknowledge the data byte output and the memory continues to output the next byte in sequence. To terminate the stream of bytes, the master must NOT acknowledge the last byte out-

## **DEVICE OPERATION** (cont'd)

put, but MUST generate a STOP condition. The output data is from consecutive byte addresses, with the internal byte address counter automatically incremented after each byte output. After a count of the last memory address, the address

counter will 'roll- over' and the memory will continue to output data.

**Acknowledge in Read Mode.** In all read modes the ST24/25x04 wait for an acknowledge during the 9th bit time. If the master does not pull the SDA line low during this time, the ST24/25x04 terminate the data transfer and switches to a standby state.

Figure 11. Read Modes Sequence

Note: \* The 7 Most Significant bits of DEV SEL bytes of a Random Read (1st byte and 3rd byte) must be identical.

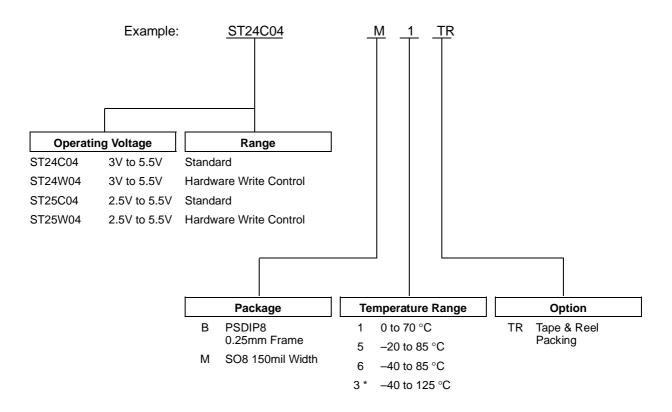

#### **ORDERING INFORMATION SCHEME**

**Notes:** 3 \* Temperature range on special request only.

Parts are shipped with the memory content set at all "1's" (FFh).

For a list of available options (Operating Voltage, Range, Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.

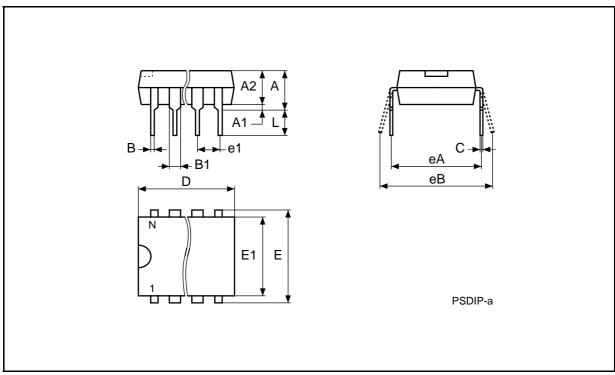

PSDIP8 - 8 pin Plastic Skinny DIP, 0.25mm lead frame

| Symb | mm   |      |       |       | inches |       |  |  |

|------|------|------|-------|-------|--------|-------|--|--|

| Cyb  | Тур  | Min  | Max   | Тур   | Min    | Max   |  |  |

| Α    |      | 3.90 | 5.90  |       | 0.154  | 0.232 |  |  |

| A1   |      | 0.49 | _     |       | 0.019  | -     |  |  |

| A2   |      | 3.30 | 5.30  |       | 0.130  | 0.209 |  |  |

| В    |      | 0.36 | 0.56  |       | 0.014  | 0.022 |  |  |

| B1   |      | 1.15 | 1.65  |       | 0.045  | 0.065 |  |  |

| С    |      | 0.20 | 0.36  |       | 0.008  | 0.014 |  |  |

| D    |      | 9.20 | 9.90  |       | 0.362  | 0.390 |  |  |

| Е    | 7.62 | -    | _     | 0.300 | _      | _     |  |  |

| E1   |      | 6.00 | 6.70  |       | 0.236  | 0.264 |  |  |

| e1   | 2.54 | _    | _     | 0.100 | _      | -     |  |  |

| eA   |      | 7.80 | _     |       | 0.307  | _     |  |  |

| eВ   |      | _    | 10.00 |       | _      | 0.394 |  |  |

| L    |      | 3.00 | 3.80  |       | 0.118  | 0.150 |  |  |

| N    |      | 8    |       |       | 8      |       |  |  |

Drawing is not to scale

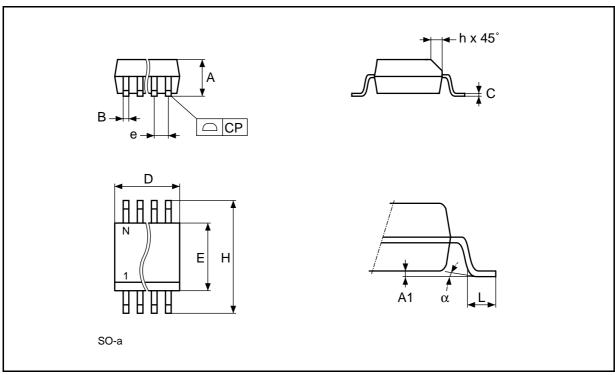

# SO8 - 8 lead Plastic Small Outline, 150 mils body width

| Symb   |      | mm   |      |       | inches |       |  |  |

|--------|------|------|------|-------|--------|-------|--|--|

| Syllib | Тур  | Min  | Max  | Тур   | Min    | Max   |  |  |

| А      |      | 1.35 | 1.75 |       | 0.053  | 0.069 |  |  |

| A1     |      | 0.10 | 0.25 |       | 0.004  | 0.010 |  |  |

| В      |      | 0.33 | 0.51 |       | 0.013  | 0.020 |  |  |

| С      |      | 0.19 | 0.25 |       | 0.007  | 0.010 |  |  |

| D      |      | 4.80 | 5.00 |       | 0.189  | 0.197 |  |  |

| E      |      | 3.80 | 4.00 |       | 0.150  | 0.157 |  |  |

| е      | 1.27 | _    | _    | 0.050 | _      | _     |  |  |

| Н      |      | 5.80 | 6.20 |       | 0.228  | 0.244 |  |  |

| h      |      | 0.25 | 0.50 |       | 0.010  | 0.020 |  |  |

| L      |      | 0.40 | 0.90 |       | 0.016  | 0.035 |  |  |

| α      |      | 0°   | 8°   |       | 0°     | 8°    |  |  |

| N      |      | 8    |      |       | 8      |       |  |  |

| СР     |      |      | 0.10 |       |        | 0.004 |  |  |

Drawing is not to scale

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - All Rights Reserved

All other names are the property of their respective owners

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.