### **INTEGRATED CIRCUITS**

### DATA SHEET

### TDA8360; TDA8361; TDA8362 Integrated PAL and PAL/NTSC TV processors

Objective specification

File under Integrated Circuits, IC02

March 1994

**Philips Semiconductors**

**PHILIPS**

### Integrated PAL and PAL/NTSC TV processors

### TDA8360; TDA8361; TDA8362

#### **FEATURES**

### Available in TDA8360, TDA8361 and TDA8362

- Vision IF amplifier with high sensitivity and good differential gain and phase

- Multistandard FM sound demodulator (4.5 MHz to 6.5 MHz)

- Integrated chrominance trap and bandpass filters (automatically calibrated)

- · Integrated luminance delay line

- RGB control circuit with linear RGB inputs and fast blanking

- Horizontal synchronization with two control loops and alignment-free horizontal oscillator without external components

- Vertical count-down circuit (50/60 Hz) and vertical preamplifier

- Low dissipation (700 mW)

- Small amount of peripheral components compared with competition ICs

- Only one adjustment (vision IF demodulator)

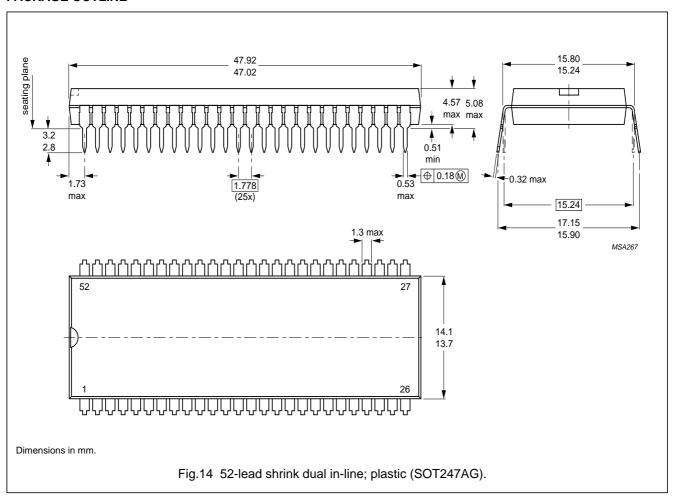

- The supply voltage for the ICs is 8 V. They are mounted in a shrink DIL envelope with 52 pins and are pin compatible.

#### Additional features

#### TDA8360

Alignment-free PAL colour decoder for all PAL standards, including PAL-N and PAL-M.

#### TDA8361

- PAL/NTSC colour decoder with automatic search system

- Source selection for external audio/video (A/V) inputs (separate Y/C signals can also be applied).

#### TDA8362

- Multistandard vision IF circuit (positive and negative modulation)

- PAL/NTSC colour decoder with automatic search system

- Source selection for external A/V inputs (separate Y/C signals can also be applied)

- Easy interfacing with the TDA8395 (SECAM decoder) for multistandard applications.

#### **GENERAL DESCRIPTION**

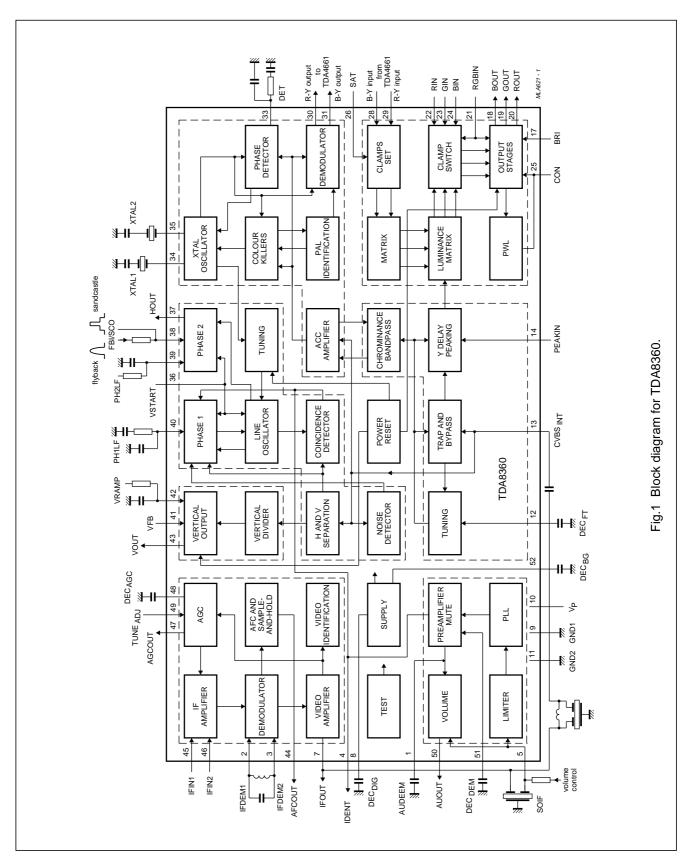

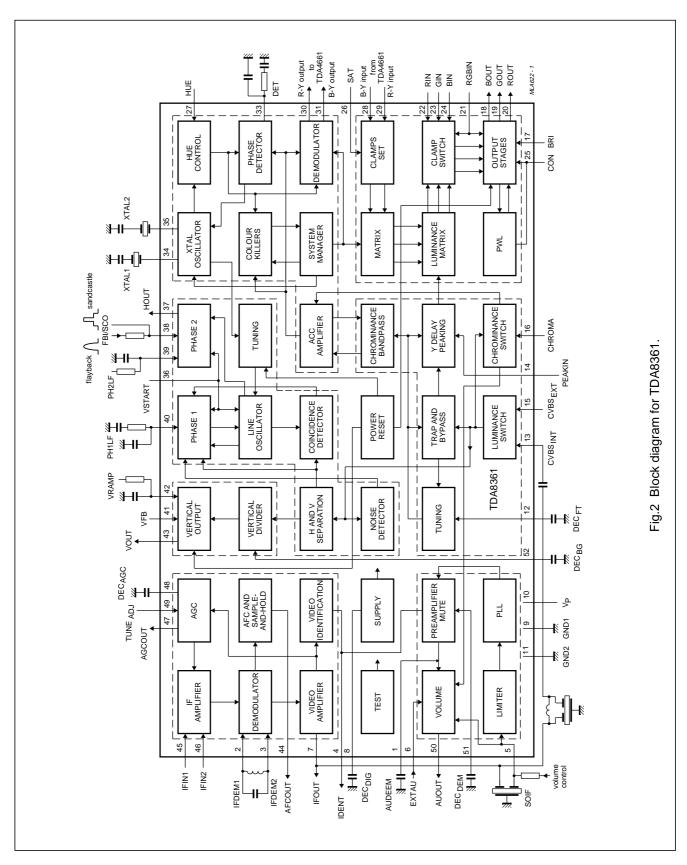

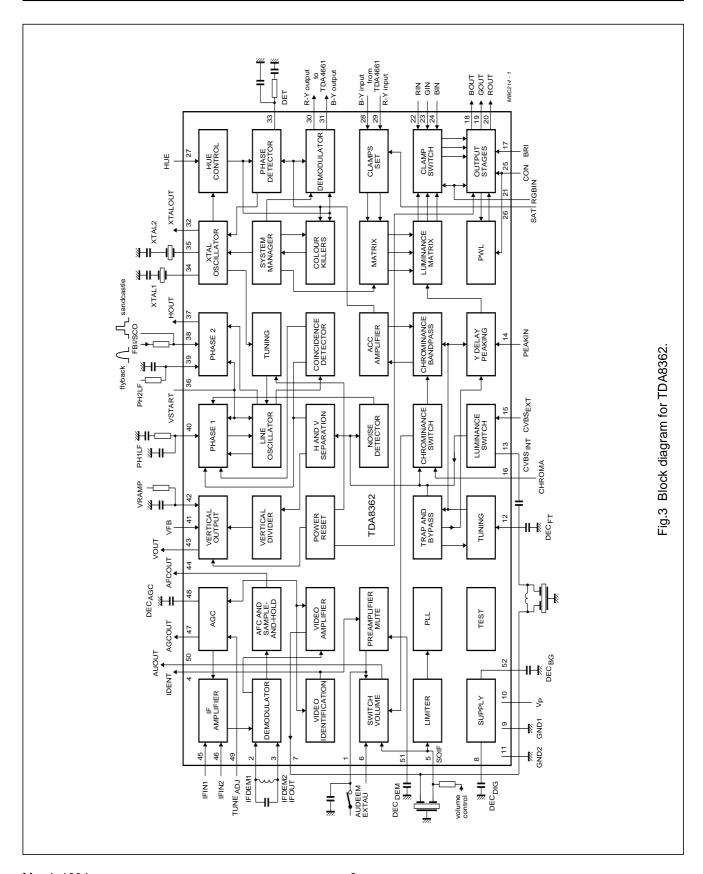

The TDA8360, TDA8361 and TDA8362 are single-chip TV processors which contain nearly all small signal functions that are required for a colour television receiver. For a complete receiver the following circuits need to be added: a base-band delay line (TDA4661), a tuner and output stages for audio, video and horizontal and vertical deflection.

Because of the different functional contents of the ICs the set maker can make the optimum choice depending on the requirements for the receiver.

The TDA8360 is intended for simple PAL receivers (all PAL standards, including PAL-N and PAL-M are possible).

The TDA8361 contains a PAL/NTSC decoder and has an A/V switch.

For real multistandard applications the TDA8362 is available. In addition to the extra functions which are available in the TDA8361, the TDA8362 can handle signals with positive modulation and it supplies the signals which are required for the SECAM decoder TDA8395.

### **ORDERING INFORMATION**

| EXTENDED TYPE | PACKAGE |              |          |          |  |

|---------------|---------|--------------|----------|----------|--|

| NUMBER        | PINS    | PIN POSITION | MATERIAL | CODE     |  |

| TDA8360       | 52      | shrink DIL   | plastic  | SOT247AG |  |

| TDA8361       | 52      | shrink DIL   | plastic  | SOT247AG |  |

| TDA8362       | 52      | shrink DIL   | plastic  | SOT247AG |  |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

### **QUICK REFERENCE DATA**

| SYMBOL                     | PARAMETER                                                                         | CONDITIONS       | MIN.     | TYP. | MAX. | UNIT |

|----------------------------|-----------------------------------------------------------------------------------|------------------|----------|------|------|------|

| V <sub>P</sub>             | supply voltage                                                                    |                  | 7.2      | 8.0  | 8.8  | V    |

| Ι <sub>P</sub>             | supply current                                                                    |                  | _        | 80   | _    | mA   |

| Input voltage              | es                                                                                |                  |          |      |      |      |

| V <sub>45,46(rms)</sub>    | video IF amplifier sensitivity (RMS value)                                        |                  | <u> </u> | 70   | 100  | μV   |

| V <sub>5(rms)</sub>        | sound IF amplifier sensitivity (RMS value)                                        |                  | Ī-       | 1    | _    | mV   |

| V <sub>6(rms)</sub>        | external audio input (RMS value)                                                  | TDA8361, TDA8362 | _        | 350  | _    | mV   |

| V <sub>15(p-p)</sub>       | external CVBS input (peak-to-peak value)                                          | TDA8361, TDA8362 | Ī-       | 1    | _    | V    |

| V <sub>22,23,24(p-p)</sub> | RGB inputs (peak-to-peak value)                                                   |                  | _        | 0.7  | _    | V    |

| Output signa               | ils                                                                               |                  |          |      |      |      |

| $V_{O(p-p)}$               | demodulated CVBS output (peak-to-peak value)                                      |                  | _        | 2.4  | _    | V    |

| I <sub>47</sub>            | tuner AGC control current                                                         |                  | 0        | _    | 5    | mA   |

| V <sub>44</sub>            | AFC output voltage swing                                                          |                  | _        | 6    | _    | V    |

| V <sub>50(rms)</sub>       | audio output voltage (RMS value)                                                  |                  | Ī-       | 700  | _    | mV   |

| V <sub>18,19,20(p-p)</sub> | RGB output signal amplitudes (peak-to-peak value)                                 |                  | _        | 4    | _    | V    |

| I <sub>37</sub>            | horizontal output current                                                         |                  | 10       | _    | _    | mA   |

| I <sub>43</sub>            | vertical output current                                                           |                  | 1        | _    | _    | mA   |

| Control volta              | iges                                                                              |                  | •        | •    | •    | •    |

| V <sub>control</sub>       | control voltages for Volume, Contrast,<br>Saturation, Brightness, Hue and Peaking |                  | 0        | _    | 5    | V    |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

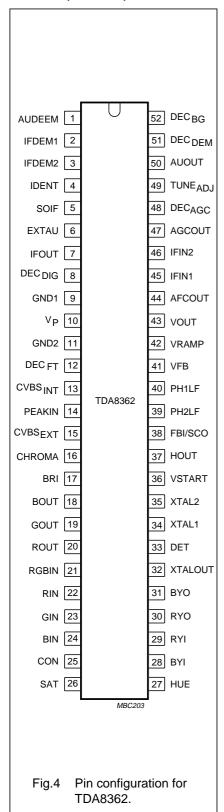

### **PINNING (TDA8362)**

| SYMBOL              | PIN | DESCRIPTION                               |

|---------------------|-----|-------------------------------------------|

| AUDEEM              | 1   | audio de-emphasis and ± modulation switch |

| IFDEM1              | 2   | IF demodulator tuned circuit              |

| IFDEM2              | 3   | IF demodulator tuned circuit              |

| IDENT               | 4   | video identification output/MUTE input    |

| SOIF                | 5   | sound IF input and volume control         |

| EXTAU               | 6   | external audio input                      |

| IFOUT               | 7   | IF video output                           |

| DEC <sub>DIG</sub>  | 8   | decoupling digital supply                 |

| GND1                | 9   | ground 1                                  |

| V <sub>P</sub>      | 10  | supply voltage (+8 V)                     |

| GND2                | 11  | ground 2                                  |

| DEC <sub>FT</sub>   | 12  | decoupling filter tuning                  |

| CVBS <sub>INT</sub> | 13  | internal CVBS input                       |

| PEAKIN              | 14  | peaking control input                     |

| CVBS <sub>EXT</sub> | 15  | external CVBS input                       |

| CHROMA              | 16  | chrominance and A/V switch input          |

| BRI                 | 17  | brightness control input                  |

| BOUT                | 18  | blue output                               |

| GOUT                | 19  | green output                              |

| ROUT                | 20  | red output                                |

| RGBIN               | 21  | RGB insertion and blanking input          |

| RIN                 | 22  | red input                                 |

| GIN                 | 23  | green input                               |

| BIN                 | 24  | blue input                                |

| CON                 | 25  | contrast control input                    |

| SAT                 | 26  | saturation control input                  |

| HUE                 | 27  | hue control input (or chrominance output) |

| BYI                 | 28  | B–Y input signal                          |

| RYI                 | 29  | R-Y input signal                          |

| RYO                 | 30  | R–Y output signal                         |

| BYO                 | 31  | B–Y output signal                         |

| XTALOUT             | 32  | 4.43 MHz output for TDA8395               |

| DET                 | 33  | loop filter burst phase detector          |

| XTAL1               | 34  | 3.58 MHz crystal connection               |

| XTAL2               | 35  | 4.43 MHz crystal connection               |

| VSTART              | 36  | supply/start horizontal oscillator        |

| HOUT                | 37  | horizontal output                         |

| FBI/SCO             | 38  | flyback input/sandcastle output           |

| PH2LF               | 39  | phase 2 loop filter                       |

| PH1LF               | 40  | phase 1 loop filter                       |

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL              | PIN | DESCRIPTION                  |

|---------------------|-----|------------------------------|

| VFB                 | 41  | vertical feedback input      |

| VRAMP               | 42  | vertical ramp generator      |

| VOUT                | 43  | vertical output              |

| AFCOUT              | 44  | AFC output                   |

| IFIN1               | 45  | IF input 1                   |

| IFIN2               | 46  | IF input 2                   |

| AGCOUT              | 47  | tuner AGC output             |

| DEC <sub>AGC</sub>  | 48  | AGC decoupling capacitor     |

| TUNE <sub>ADJ</sub> | 49  | tuner take-over adjustment   |

| AUOUT               | 50  | audio output                 |

| DEC <sub>DEM</sub>  | 51  | decoupling sound demodulator |

| DEC <sub>BG</sub>   | 52  | decoupling bandgap supply    |

#### **TDA8360**

The TDA8360 has the following differences to the pinning:

Pin 6: external audio input not connected

Pin 15: external CVBS input not connected

Pin 16: chrominance and A/V switch input not connected

Pin 27: hue control input not connected.

### **TDA8361**

The TDA8361 has the following differences to the pinning:

Pin 1: only audio de-emphasis

Pin 27: only hue control

Pin 32: 4.43 MHz output for TDA8395 is not connected.

### **FUNCTIONAL DESCRIPTION**

#### Video IF amplifier

The IF amplifier contains 3 AC-coupled control stages with a total gain control range of greater than 60 dB. The sensitivity of the circuit is comparable with that of modern IF ICs.

The reference carrier for the video demodulator is obtained by means of passive regeneration of the picture carrier. The external reference tuned circuit is the only remaining adjustment of the IC.

In the TDA8362 the polarity of the demodulator can be switched so that the circuit is suitable for both positive and negative modulated signals.

The AFC circuit is driven with the same reference signal as the video demodulator. To ensure that the video content does not disturb the AFC operation a sample-and-hold circuit is incorporated; the capacitor for this function is internal. The AFC output voltage is 6 V.

The AGC detector operates on levels, top sync for negative modulated and top white for positive modulated signals. The AGC detector time constant capacitor is connected externally. This is mainly because of the flexibility of the application.

The time constant of the AGC system during positive modulation (TDA8362) is slow, this is to avoid any visible picture variations. This, however, causes the system to react very slowly to sudden changes in the input signal amplitude.

To overcome this problem a speed-up circuit has been included which detects whether the AGC detector is activated every frame period. If, during a 3-frame period, no action is detected the speed of the system is increased. When the incoming signal has no peak white information (e.g. test lines in the vertical retrace period) the gain would be video signal dependent. To avoid this effect the circuit also contains a black level AGC detector which is activated when the black level of the video signal exceeds a certain level.

The TDA8361 and TDA8362 contain a video identification circuit which is independent of the synchronization circuit. Therefore search tuning is possible when the display section of the receiver is used as a monitor. In the TDA8360 this circuit is only used for stable OSD at no signal input. In the normal television mode the identification output is connected to the coincidence detector, this applies to all three devices. The identification output voltage is LOW when no transmitter is identified. In this condition the sound demodulator is switched off (mute function). When a transmitter is identified the output voltage is HIGH. The voltage level is dependent on the frequency of the incoming chrominance signal.

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

#### Sound circuit

The sound bandpass and trap filters have to be connected externally. The filtered intercarrier signal is fed to a limiter circuit and is demodulated by means of a PLL demodulator. The PLL circuit tunes itself automatically to the incoming signal, consequently, no adjustment is required.

The volume is DC controlled. The composite audio output signal has an amplitude of 700 mV RMS at a volume control setting of –6 dB. The de-emphasis capacitor has to be connected externally. The non-controlled audio signal can be obtained from this pin via a buffer stage. The amplitude of this signal is 350 mV RMS.

The TDA8361 and TDA8362 external audio input signal must have an amplitude of 350 mV RMS. The audio/video switch is controlled via the chrominance input pin.

### Synchronization circuit

The sync separator is preceded by a voltage controlled amplifier which adjusts the sync pulse amplitude to a fixed level. The sync pulses are then fed to the slicing stage (separator) which operates at 50% of the amplitude.

The separated sync pulses are fed to the first phase detector and to the coincidence detector. The coincidence detector is used for transmitter identification and to detect whether the line oscillator is synchronized. When the circuit is not synchronized the voltage on the peaking control pin (pin 14) is LOW so that this condition can be detected externally. The first PLL has a very high static steepness, this ensures that the phase of the picture is independent of the line frequency. The line oscillator operates at twice the line frequency.

The oscillator network is internal. Because of the spread of internal components an automatic adjustment circuit has been added to the IC. The circuit compares the oscillator frequency with that of the crystal oscillator in the colour decoder. This results in a free-running frequency which deviates less than 2% from the typical value.

The circuit employs a second control loop to generate the drive pulses for the horizontal driver stage.

X-ray protection can be realised by switching the pin of the second control loop to the positive supply line. The detection circuit must be connected externally. When the X-ray protection is active the horizontal output voltage is switched to a high level. When the voltage on this pin returns to its normal level the horizontal output is released again.

The IC contains a start-up circuit for the horizontal oscillator. When this feature is required a current of 6.5 mA has to be supplied to pin 36. For an application without start-up both supply pins (10 and 36) must be connected to the 8 V supply line.

The drive signal for the vertical ramp generator is generated by means of a divider circuit. The RC network for the ramp generator is external.

### Integrated video filters

The circuit contains a chrominance bandpass and trap circuit. The filters are realised by means of gyrator circuits and are automatically tuned by comparing the tuning frequency with the crystal frequency of the decoder.

In the TDA8361 and TDA8362 the chrominance trap is active only when the separate chrominance input pin is connected to ground or to the positive supply voltage and when a colour signal is recognized.

When the pin is left open-circuit the trap is switched off so that the circuit can also be used for S-VHS applications.

The luminance delay line and the delay for the peaking circuit are also realised by means of gyrator circuits.

#### Colour decoder

The colour decoder in the various ICs contains an alignment-free crystal oscillator, a colour killer circuit and colour difference demodulators. The 90° phase shift for the reference signal is achieved internally. Because the main differences of the 3 ICs are found in the colour decoder the various types will be discussed.

### **TDA8360**

This IC contains only a PAL decoder. Depending on the frequency of the crystals which are connected to the IC the decoder can demodulate all PAL standards. Because the horizontal oscillator is calibrated by using the crystal frequency as a reference the 4.4 MHz crystal must be connected to pin 35 and the 3.5 MHz crystal to pin 34. When only one crystal is connected to the IC the other crystal pin must be connected to the positive supply rail via a 47 k $\Omega$  resistor. For applications with two 3.5 MHz crystals both must be connected to pin 34 and the switching between the crystals must be made externally. Switching of the crystals is only allowed directly after the vertical retrace. The circuit will indicate whether a PAL signal has been identified by the colour decoder via the saturation control pin.

When two crystals are connected to the IC the output voltage of the video identification circuit indicates the frequency of the incoming chrominance signal.

### Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

The conditions are:

- Signal identified at f<sub>osc</sub> = 3.6 MHz; V<sub>O</sub> = 6 V

- Signal identified at f<sub>osc</sub> = 4.4 MHz (or no colour); V<sub>O</sub> = 8 V.

This information can be used to switch the sound bandpass filter and trap filter.

#### **TDA8361**

This IC contains an automatic PAL/NTSC decoder. The conditions for connecting the reference crystals are the same as for the TDA8360. The decoder can be forced to PAL when the hue control pin is connected to the positive supply voltage via a 5 k $\Omega$  or 10 k $\Omega$  resistor (approximately). The decoder cannot be forced to the NTSC standard. It is also possible to see if a colour signal is recognized via the saturation pin.

### **TDA8362**

In addition to the possibilities of the TDA8361, the TDA8362 can co-operate with the SECAM add-on decoder TDA8395.

The communication between the two ICs is achieved via pin 32. The TDA8362 supplies the reference signal (4.43 MHz) for the calibration system of the TDA8395, identification of the colour standard is via the same connection. When a SECAM signal is detected by the TDA8395 the IC will draw a current of 150  $\mu A$ . When TDA8362 has not identified a colour signal in this condition it will go into the SECAM mode, that means it will switch off the R–Y and B–Y outputs and increase the voltage level on pin 32.

This voltage will switch off the colour-killer in the TDA8395 and switch on the R-Y and B-Y outputs of the TDA8395. Forcing the system to the SECAM standard can be achieved by loading pin 32 with a current of 150  $\mu$ A. Then the system manager in the TDA8362 will not search for PAL or NTSC signals. Forcing to NTSC is not possible. For PAL/SECAM applications the input signal for the TDA8395 can be obtained from pin 27 (hue control) when this pin is connected to the positive supply rail via the 5 k $\Omega$  or 10 k $\Omega$  resistor. An external source selector is required by the TDA8395/TDA8362 combination for PAL/SECAM/NTSC applications.

### **RGB** output circuit

The colour difference signals are matrixed with the luminance signal to obtain the RGB signals. Linear amplifiers have been chosen for the RGB inputs so that the circuit is suitable for incoming signals from the SCART connector. The contrast and brightness controls operate on internal and external signals.

The fast blanking pin has a second detection level at 3.5 V. When this level is exceeded the RGB outputs are blanked so that "On-Screen-Display" signals can be applied to the outputs. The output signal has an amplitude of approximately 4 V, black-to-white, with nominal input signals and nominal control settings. The nominal black level is 1.3 V.

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC134).

| SYMBOL           | PARAMETER                                | MIN. | MAX. | UNIT |

|------------------|------------------------------------------|------|------|------|

| V <sub>P</sub>   | supply voltage                           | _    | 9.0  | V    |

| T <sub>stg</sub> | storage temperature                      | -25  | +150 | °C   |

| T <sub>amb</sub> | operating ambient temperature            | -25  | +70  | °C   |

| T <sub>sol</sub> | soldering temperature for 5 s            | _    | 260  | °C   |

| Tj               | maximum junction temperature (operating) | _    | 150  | °C   |

### THERMAL RESISTANCE

| SYMBOL              | PARAMETER                            | THERMAL RESISTANCE |

|---------------------|--------------------------------------|--------------------|

| R <sub>th j-a</sub> | from junction to ambient in free air | 40 K/W             |

### **CHARACTERISTICS**

$V_P$  = 8 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL              | PARAMETER                                    | CONDITIONS                 | MIN. | TYP. | MAX. | UNIT |

|---------------------|----------------------------------------------|----------------------------|------|------|------|------|

| Supplies            |                                              | •                          |      | •    |      | •    |

| V <sub>P</sub>      | supply voltage (pin 10)                      |                            | 7.2  | 8.0  | 8.8  | V    |

| I <sub>P</sub>      | supply current (pin 10)                      |                            | _    | 80   | _    | mA   |

| I <sub>HOSC</sub>   | horizontal oscillator start current (pin 36) | note 1                     | 6.5  | _    | _    | mA   |

| P <sub>tot</sub>    | total power dissipation                      | including start supply     | _    | 0.7  | _    | W    |

| IF circuit          |                                              | •                          |      | •    | •    | •    |

| VISION IF AMP       | LIFIER INPUTS (PINS 45 AND 46)               |                            |      |      |      |      |

| V <sub>i(rms)</sub> | input sensitivity (RMS value)                | note 2                     |      |      |      |      |

|                     |                                              | $f_i = 38.90 \text{ MHz}$  | _    | 70   | 100  | μV   |

|                     |                                              | f <sub>i</sub> = 45.75 MHz | _    | 70   | 100  | μV   |

|                     |                                              | $f_i = 58.75 \text{ MHz}$  | _    | 70   | 100  | μV   |

| R <sub>I</sub>      | Input resistance (differential)              | note 3                     | _    | 2    | _    | kΩ   |

| C <sub>I</sub>      | Input capacitance (differential)             | note 3                     | _    | 3    | _    | pF   |

| G <sub>cr</sub>     | gain control range                           |                            | 64   | _    | _    | dB   |

| V <sub>i(rms)</sub> | maximum input signal (RMS value)             |                            | 100  | _    | _    | mV   |

# Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL                | PARAMETER                                                                                            | CONDITIONS                               | MIN. | TYP. | MAX. | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------------|------------------------------------------|------|------|------|------|

| VIDEO AMPLIF          | IER OUTPUT; NOTE 4 (PIN 7)                                                                           |                                          |      |      |      |      |

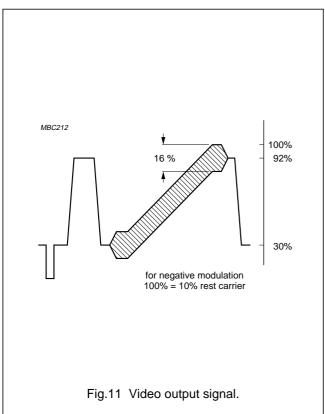

| V <sub>7</sub>        | negative modulation                                                                                  |                                          |      |      |      |      |

|                       | zero signal output level                                                                             | note 5                                   | 4.45 | 4.6  | 4.75 | V    |

|                       | top sync level                                                                                       |                                          | 1.9  | 2    | 2.1  | V    |

| V <sub>7</sub>        | positive modulation (TDA8362)                                                                        |                                          |      |      |      |      |

|                       | zero signal output level                                                                             | note 5                                   | 1.85 | 2    | 2.15 | V    |

|                       | white level                                                                                          |                                          | 4.2  | 4.3  | 4.4  | V    |

| $\Delta V_7$          | difference in amplitude between negative and positive modulation                                     |                                          | _    | 0    | 15   | %    |

| V <sub>7</sub>        | detection level of black level for positive modulation when no peak white is available in the signal |                                          | _    | 3.1  | _    | V    |

| Z <sub>O</sub>        | video output impedance                                                                               |                                          | _    | _    | 50   | Ω    |

| l <sub>bias</sub>     | internal bias current of NPN emitter follower output transistor                                      |                                          | 1    | _    | _    | mA   |

| I <sub>source</sub>   | maximum source current                                                                               |                                          | _    | _    | 5    | mA   |

| В                     | bandwidth of demodulated output signal                                                               | -3 dB                                    | 6    | 9    | _    | MHz  |

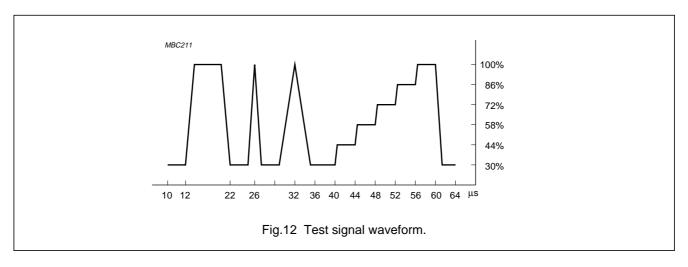

| G <sub>diff</sub>     | gain differential                                                                                    | note 6                                   | _    | 2    | 5    | %    |

| $\Phi_{diff}$         | phase differential                                                                                   | notes 6 and 7                            | _    | 1    | 5    | deg  |

| NL <sub>vid</sub>     | video non linearity                                                                                  | note 8                                   | _    | _    | 5    | %    |

| $V_{th}$              | white spot threshold voltage level                                                                   |                                          | _    | 4.8  | _    | V    |

| $V_{\text{ins}}$      | white spot insertion voltage level                                                                   |                                          | _    | 3.2  | _    | V    |

| N <sub>clamp</sub>    | noise inverter clamping voltage level                                                                |                                          | _    | 1.4  | _    | V    |

| N <sub>ins</sub>      | noise inverter insertion level                                                                       | note 9                                   | _    | 2.6  | _    | V    |

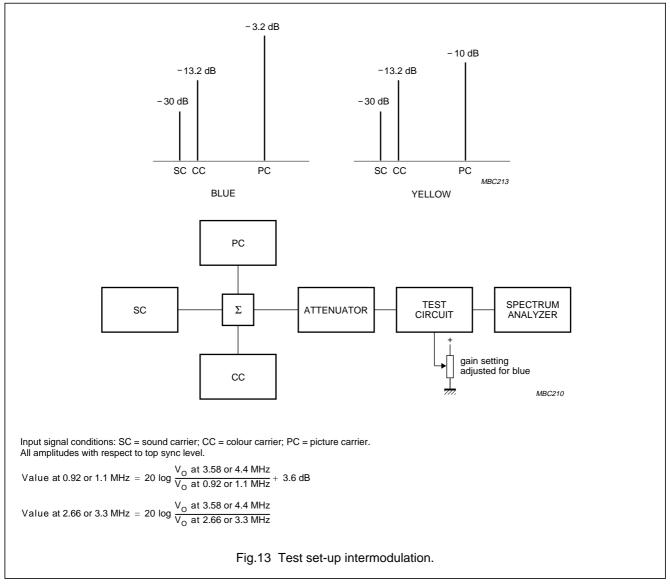

| $\delta_{\text{mod}}$ | intermodulation                                                                                      | notes 7 and 10                           |      |      |      |      |

|                       | blue                                                                                                 | $V_0 = 0.92 \text{ or } 1.1 \text{ MHz}$ | 60   | 66   | _    | dB   |

|                       | yellow                                                                                               | $V_0 = 0.92 \text{ or } 1.1 \text{ MHz}$ | 56   | 62   | _    | dB   |

|                       | blue                                                                                                 | $V_0 = 2.66 \text{ or } 3.3 \text{ MHz}$ | 60   | 66   | _    | dB   |

|                       | yellow                                                                                               | $V_0 = 2.66 \text{ or } 3.3 \text{ MHz}$ | 60   | 66   | _    | dB   |

| S/N                   | signal-to-noise ratio                                                                                | notes 7 and 11                           |      |      |      |      |

|                       |                                                                                                      | V <sub>i</sub> = 10 mV                   | 52   | 60   | _    | dB   |

|                       |                                                                                                      | end of control range                     | 52   | 61   | _    | dB   |

| V <sub>7</sub>        | residual carrier signal                                                                              | note 7                                   | _    | 1    | _    | mV   |

| V <sub>7</sub>        | residual 2nd harmonic of carrier signal                                                              | note 7                                   | _    | 0.5  | _    | mV   |

# Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL               | PARAMETER                                                                                             | CONDITIONS                              | MIN. | TYP. | MAX.               | UNIT   |

|----------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|------|------|--------------------|--------|

| IF AND TUNER         | AGC; NOTE 12                                                                                          |                                         | !    | !    | ·!                 |        |

| Timing of IF-        | AGC (C48 = 2.2 μF)                                                                                    |                                         |      |      |                    |        |

|                      | modulated video interference                                                                          | 30% AM for 1 to<br>100 mV; 0 to 200 Hz  | _    | _    | 10                 | %      |

| t <sub>inc</sub>     | response time for an IF input signal amplitude increase of 52 dB for positive and negative modulation |                                         | _    | 2    | _                  | ms     |

| t <sub>dec</sub>     | response time for an IF input signal amplitude decrease of 52 dB                                      |                                         |      |      |                    |        |

|                      | for negative modulation                                                                               |                                         | _    | 25   | _                  | ms     |

|                      | for positive modulation (TDA8362)                                                                     |                                         | _    | 100  | _                  | ms     |

| I <sub>leak</sub>    | allowed leakage current of the AGC capacitor                                                          | note 13                                 |      |      |                    |        |

|                      | for negative modulation                                                                               |                                         | _    | _    | 10                 | μΑ     |

|                      | for positive modulation                                                                               |                                         | _    | _    | 200                | nA     |

| Tuner take-o         | ver adjustment (pin 49)                                                                               |                                         |      |      |                    |        |

| V <sub>49(rms)</sub> | minimum starting level voltage for tuner take-over (RMS value)                                        |                                         | _    | 0.2  | 0.5                | mV     |

| V <sub>49(rms)</sub> | maximum starting level voltage for tuner take-over (RMS value)                                        |                                         | 100  | 150  | _                  | mV     |

| V <sub>cr</sub>      | control voltage range                                                                                 |                                         | 0.5  | _    | 4.5                | V      |

| Tuner control        | output (pin 47)                                                                                       |                                         |      |      |                    |        |

| V <sub>47</sub>      | maximum tuner AGC output voltage                                                                      | maximum gain                            | _    | _    | V <sub>P</sub> + 1 | V      |

| V <sub>47(sat)</sub> | output saturation voltage                                                                             | minimum gain;<br>I <sub>47</sub> = 2 mA | _    | _    | 300                | mV     |

| I <sub>47</sub>      | maximum tuner AGC output swing                                                                        |                                         | 5    | _    | _                  | mA     |

| I <sub>leak</sub>    | leakage current RF AGC                                                                                |                                         | _    | _    | 1                  | μΑ     |

| $\Delta V_{47}$      | input signal variation for complete tuner control                                                     | $I_{O(max)} = 1 \text{ mA}$             | 1    | 2    | 4                  | dB     |

| AFC OUTPUT;          | NOTE 14 (PIN 44)                                                                                      |                                         |      |      |                    | •      |

| V <sub>44</sub>      | output voltage swing                                                                                  |                                         | _    | 6    | _                  | V      |

| f <sub>sl</sub>      | AFC slope                                                                                             |                                         | _    | 33   | _                  | mV/kHz |

| f <sub>os</sub>      | AFC offset                                                                                            | note 7                                  | _    | _    | 50                 | kHz    |

| Vo                   | output voltage at centre frequency                                                                    |                                         | _    | 3.5  | _                  | V      |

| Z <sub>O</sub>       | output impedance                                                                                      |                                         | _    | 50   | _                  | kΩ     |

| SWITCHING TO         | POSITIVE MODULATION (TDA8362); NOTE                                                                   | 15 (PIN 1)                              |      |      |                    |        |

| V <sub>1</sub>       | minimum voltage on pin 1 to switch<br>the video demodulator and AGC to<br>positive modulation         |                                         | _    | _    | V <sub>P</sub> – 1 | V      |

| I <sub>I</sub>       | input current                                                                                         |                                         | _    | _    | 1                  | mA     |

# Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL               | PARAMETER                                                                            | CONDITIONS                                                                                 | MIN. | TYP. | MAX. | UNIT |

|----------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| VIDEO IDENT          | iFICATION OUTPUT (PIN 4)                                                             | 1                                                                                          |      |      |      | -    |

| Vo                   | output voltage                                                                       | video not identified                                                                       | _    | _    | 0.5  | V    |

| Z <sub>O</sub>       | output impedance                                                                     |                                                                                            | _    | 25   | _    | kΩ   |

| Vo                   | output voltage                                                                       | video identified;<br>colour signal<br>available;<br>f <sub>osc</sub> = 3.5 MHz             | -    | 6    | -    | V    |

|                      |                                                                                      | video identified;<br>colour signal<br>available/unavailable<br>;f <sub>osc</sub> = 4.4 MHz | _    | 8    | _    | V    |

| t <sub>d</sub>       | delay time of identification after<br>the AGC has stabilized on a new<br>transmitter |                                                                                            | _    | _    | 10   | ms   |

| I <sub>4</sub>       | maximum load current at pin 4                                                        |                                                                                            | _    | _    | 25   | μΑ   |

| Sound circu          | <br>uit                                                                              |                                                                                            |      |      |      |      |

| DEMODULATO           | DR INPUT; NOTE 16 (PIN 5)                                                            |                                                                                            |      |      |      |      |

| V <sub>5(rms)</sub>  | input limiting for PLL catching range (RMS value)                                    |                                                                                            | _    | 1    | 2    | mV   |

| Δf                   | catching range PLL                                                                   | note 17                                                                                    | 4.2  | _    | 6.8  | MHz  |

| R <sub>I</sub>       | DC input resistance                                                                  | note 3                                                                                     | 100  | _    | _    | kΩ   |

| C <sub>I</sub>       | input capacitance                                                                    | note 3                                                                                     | _    | 15   | _    | pF   |

| AMR                  | AM rejection                                                                         | V <sub>I</sub> = 50 mV RMS;<br>note 18                                                     | 60   | 66   | _    | dB   |

| DE-EMPHASIS          | S (PIN 1)                                                                            |                                                                                            |      |      |      |      |

| V <sub>O(rms)</sub>  | output signal amplitude (RMS value)                                                  | note 17                                                                                    | _    | 350  | _    | mV   |

| R <sub>O</sub>       | output resistance                                                                    |                                                                                            | _    | 15   | _    | kΩ   |

| V <sub>1</sub>       | DC output voltage                                                                    |                                                                                            | _    | 3    | _    | V    |

| AUDIO ATTEN          | IUATOR OUTPUT (PIN 50)                                                               |                                                                                            |      | •    | •    | •    |

| V <sub>50(rms)</sub> | controlled output signal amplitude (RMS value)                                       | -6 dB; note 17                                                                             | 500  | 700  | 900  | mV   |

| R <sub>O</sub>       | output resistance                                                                    |                                                                                            | _    | 250  | _    | Ω    |

| V <sub>50</sub>      | DC output voltage                                                                    |                                                                                            | _    | 3.3  | _    | V    |

| THD                  | total harmonic distortion                                                            | note 19                                                                                    | _    | _    | 0.5  | %    |

| S/N <sub>int</sub>   | internal signal-to-noise ratio                                                       | note 7                                                                                     | _    | 60   | _    | dB   |

| S/N <sub>ext</sub>   | external signal-to-noise ratio                                                       | note 7                                                                                     | _    | 80   | _    | dB   |

| VOL <sub>cr</sub>    | control range                                                                        | see also Fig.5                                                                             | _    | 80   | _    | dB   |

| OSS                  | suppression of output signal when mute is active                                     |                                                                                            | _    | 80   | _    | dB   |

| $\Delta V_{50}$      | DC shift of the output when mute is active                                           | note 20                                                                                    | _    | 10   | 50   | mV   |

# Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL               | PARAMETER                                                                | CONDITIONS       | MIN.                 | TYP. | MAX. | UNIT |

|----------------------|--------------------------------------------------------------------------|------------------|----------------------|------|------|------|

| EXTERNAL AUI         | DIO INPUT (TDA8361, TDA8362); NOTE 21                                    | (PIN 6)          | !                    | '    | !    | -!   |

| V <sub>6(rms)</sub>  | input signal amplitude (RMS value)                                       |                  | _                    | 350  | 700  | mV   |

| R <sub>I</sub>       | input resistance                                                         |                  | _                    | 25   | -    | kΩ   |

| $\Delta G_V$         | voltage gain difference between input and output                         | maximum volume   | _                    | 12   | _    | dB   |

| $\alpha_{cr}$        | crosstalk between internal and external audio signals                    |                  | 60                   | _    | _    | dB   |

| CVBS/On-Sc           | reen Display and CD inputs                                               |                  |                      |      |      |      |

| INTERNAL AND         | EXTERNAL CVBS INPUTS (PINS 13 AND 15                                     | )                |                      |      |      |      |

| V <sub>13(p-p)</sub> | internal CVBS input voltage (peak-to-peak value)                         | notes 3 and 22   | -                    | 2    | 2.8  | V    |

| I <sub>13</sub>      | internal CVBS input current                                              |                  | _                    | 4    | _    | μΑ   |

| V <sub>15(p-p)</sub> | external CVBS input voltage;<br>TDA8361, TDA8362<br>(peak-to-peak value) | note 3           | -                    | 1    | 1.4  | V    |

| I <sub>15</sub>      | external CVBS input current;<br>TDA8361, TDA8362                         |                  | _                    | 4    | -    | μΑ   |

| ISS                  | suppression of non-selected CVBS input signal; TDA8361, TDA8362          | note 23          | 50                   | _    | _    | dB   |

| COMBINED CH          | ROMINANCE AND SWITCH INPUT (TDA8361,                                     | TDA8362; PIN 16) |                      |      |      |      |

| V <sub>16(p-p)</sub> | chrominance input voltage (peak-to-peak value)                           | notes 3 and 24   | _                    | 0.3  | _    | V    |

| V <sub>16(p-p)</sub> | input signal amplitude before clipping occurs (peak-to-peak value)       | note 7           | 1                    | _    | _    | V    |

| R <sub>I</sub>       | chrominance input resistance                                             |                  | _                    | 15   | _    | kΩ   |

| C <sub>I</sub>       | chrominance input capacitance                                            | note 3           | _                    | _    | 5    | pF   |

| V <sub>16</sub>      | DC input voltage to switch the A/V switch to internal mode               |                  | _                    | _    | 0.5  | V    |

| V <sub>16</sub>      | DC input voltage to switch the A/V switch to external mode               |                  | V <sub>P</sub> – 0.5 | _    | _    | V    |

| V <sub>16</sub>      | DC input voltage for chrominance insertion                               |                  | 3                    | 4    | 5    | V    |

| SS <sub>CVBS</sub>   | suppression of non-selected chrominance signal from CVBS input           | notes 7 and 23   | 50                   | _    | -    | dB   |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL                     | PARAMETER                                                                                                       | CONDITIONS        | MIN. | TYP.            | MAX. | UNIT |

|----------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|------|-----------------|------|------|

| RGB INPUTS F               | FOR ON-SCREEN DISPLAY (PINS 22, 23 AND                                                                          | 24)               |      | !               | !    |      |

| V <sub>22,23,24(p-p)</sub> | input signal amplitude for an output<br>signal of 4V (black-to-white)<br>(peak-to-peak value)                   | note 25           | _    | 0.7             | 0.8  | V    |

| V <sub>22,23,24(p-p)</sub> | input signal amplitude before clipping occurs (peak-to-peak value)                                              |                   | 1    | _               | _    | V    |

| V <sub>diff</sub>          | difference of black level of internal and external signals at the outputs                                       |                   | _    | _               | 100  | mV   |

| I <sub>22,23,24</sub>      | input currents                                                                                                  |                   | _    | 0.1             | _    | μΑ   |

| FAST BLANKING              | G (PIN 21)                                                                                                      |                   |      |                 |      | •    |

| V <sub>I</sub>             | fast blanking input voltage                                                                                     | no data insertion | _    | <u> </u>        | 0.4  | V    |

| VI                         | fast blanking input voltage                                                                                     | data insertion    | 0.9  | _               | _    | V    |

| V <sub>21(max)</sub>       | maximum input pulse                                                                                             | data insertion    | _    | Ī-              | 3    | V    |

| t <sub>d</sub>             | delay of data insertion                                                                                         |                   | _    | -               | 20   | ns   |

| I <sub>21</sub>            | input current                                                                                                   |                   | _    | 0.2             | _    | mA   |

| SS <sub>int</sub>          | suppression of internal RGB signals with data insertion at f = 0 to 5 MHz                                       | note 23           | 46   | -               | _    | dB   |

| SS <sub>ext</sub>          | suppression of external RGB signals with data insertion at f = 0 to 5 MHz                                       | note 23           | 46   | -               | _    | dB   |

| VI                         | input voltage to blank the RGB outputs to facilitate 'On-Screen-Display' signals being applied to these outputs | note 26           | 4    | -               | -    | V    |

| t <sub>d</sub>             | delay between the input pulse and the blanking at the output                                                    | note 7            | -    | 30              | -    | ns   |

| COLOUR DIFFE               | ERENCE INPUT SIGNALS (PINS 28 AND 29)                                                                           |                   |      | •               | •    |      |

| V <sub>29(p-p)</sub>       | input signal amplitude (R–Y) (peak-to-peak value)                                                               |                   | _    | 1.05            | -    | V    |

| V <sub>28(p-p)</sub>       | input signal amplitude (B-Y) (peak-to-peak value)                                                               |                   | -    | 1.35            | -    | V    |

| I <sub>28,29</sub>         | input current for both inputs                                                                                   |                   | _    | 0.1             | 1.0  | μΑ   |

| Chrominance                | e filters                                                                                                       |                   |      |                 |      |      |

| CHROMINANCE                | TRAP CIRCUIT                                                                                                    |                   |      |                 |      |      |

| f <sub>trap</sub>          | trap frequency                                                                                                  |                   |      | f <sub>SC</sub> | _    | MHz  |

| QF                         | trap quality factor                                                                                             | notes 7 and 27    | _    | 2               | _    |      |

| SR                         | colour subcarrier rejection                                                                                     |                   | 20   | _               | _    | dB   |

| CHROMINANCE                | E BANDPASS CIRCUIT                                                                                              | 1                 |      |                 | -1   | 1    |

| f <sub>c</sub>             | centre frequency                                                                                                |                   |      | f <sub>SC</sub> | _    | MHz  |

| QBP                        | bandpass quality factor                                                                                         | note 7            |      | 3               | _    |      |

|                            |                                                                                                                 | 1                 |      | 1               | 1    | 1    |

# Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL                        | PARAMETER                                                                                    | CONDITIONS                           | MIN. | TYP.  | MAX. | UNIT |

|-------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------|------|-------|------|------|

| Delay line an                 | d peaking circuit                                                                            |                                      | !    | -     | •    |      |

| Y DELAY LINE                  |                                                                                              |                                      |      |       |      |      |

| t <sub>d</sub>                | delay time                                                                                   | note 7                               | _    | 480   | _    | ns   |

| В                             | bandwidth of internal delay line                                                             | note 7                               | 8    | _     | _    | MHz  |

| PEAKING CONT                  | ROL; NOTE 28, SEE ALSO FIG.6 (PIN 14)                                                        |                                      | •    |       | •    | •    |

| t <sub>W</sub>                | width of preshoot or overshoot                                                               | at 50% of pulse;<br>note 7           | _    | 160   | -    | ns   |

| S <sub>cth</sub>              | peaking signal compression threshold                                                         |                                      | _    | 50    | -    | IRE  |

| I <sub>14</sub>               | input current when no video input signal present                                             |                                      | _    | 1     | -    | mA   |

| VI                            | voltage level to switch off peaking                                                          |                                      | _    | 7     | _    | V    |

| Horizontal ar                 | nd vertical synchronization circuits                                                         |                                      |      |       |      |      |

| SYNC VIDEO IN                 | IPUT (TDA8361, TDA8362; PINS 13 AND 15                                                       | 5)                                   |      |       |      |      |

| V <sub>13</sub>               | sync pulse amplitude                                                                         | referenced to pin 15;<br>note 3      | 50   | 300   | -    | mV   |

| SL                            | slicing level                                                                                | note 29                              | _    | 50    | _    | %    |

| VERTICAL SYNO                 | 5                                                                                            |                                      | •    | •     | •    | •    |

| t <sub>W</sub>                | width of the vertical sync pulse without sync instability                                    | note 30                              | 22   | -     | -    | μs   |

| HORIZONTAL C                  | SCILLATOR                                                                                    |                                      |      | •     | •    | •    |

| f <sub>fr</sub>               | free running frequency                                                                       | note 44                              | _    | 15625 | _    | Hz   |

| $\Delta f_{fr}$               | spread on free running frequency                                                             |                                      | _    | _     | ±2   | %    |

| $\Delta f_{osc}/\Delta V_{P}$ | frequency variation with respect to the supply voltage                                       | V <sub>P</sub> = 8 V ±10%;<br>note 7 | _    | 0.2   | 0.5  | %    |

| $\Delta f_{osc}/\Delta T$     | frequency variation with temperature                                                         | $T_{amb}$ = 25 °C ±50 °C;<br>note 7  | _    | 1     | _    | Hz/K |

| $\Delta f_{\rm osc(\ max)}$   | maximum frequency deviation at the start of the horizontal output                            |                                      | _    | _     | 75   | %    |

| FIRST CONTRO                  | L LOOP; NOTE 31 (FILTER CONNECTED TO                                                         | PIN 40)                              |      |       |      |      |

| f <sub>HR</sub>               | holding range PLL                                                                            |                                      | _    | ±0.9  | ±1.2 | kHz  |

| f <sub>CR</sub>               | catching range PLL                                                                           | note 7                               | ±0.6 | ±0.9  | _    | kHz  |

| S/N                           | signal-to-noise ratio of the video input<br>signal at which the time constant is<br>switched |                                      | _    | 20    | _    | dB   |

| HYS                           | hysteresis at the switching point                                                            |                                      | _    | 3     | _    | dB   |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL                                          | PARAMETER                                                | CONDITIONS                       | MIN. | TYP.    | MAX.           | UNIT  |

|-------------------------------------------------|----------------------------------------------------------|----------------------------------|------|---------|----------------|-------|

| SECOND CONT                                     | TROL LOOP; NOTE 32 (CAPACITOR CONNEC                     | TED TO PIN 39)                   |      |         |                |       |

| $\Delta \phi_i / \Delta \phi_o$                 | control sensitivity                                      | without R <sub>L</sub> on pin 39 | _    | 150     | _              | μs/μs |

| t <sub>cr</sub>                                 | control range from start of horizontal output to flyback |                                  | 11   | 12      | _              | μs    |

| t <sub>shift</sub>                              | maximum horizontal shift range                           | note 7                           | ±2   | _       | _              | μs    |

| $\Delta \phi_{\text{i}}/\Delta \phi_{\text{o}}$ | shift control sensitivity                                | note 7                           | _    | 3       | _              | μΑ/μs |

| V <sub>39</sub>                                 | voltage to switch on the X-ray protection                |                                  | 6    | -       | _              | V     |

| lı                                              | input current during protection                          |                                  | _    | _       | tbf            | μΑ    |

| HORIZONTAL C                                    | DUTPUT (PIN 37)                                          | •                                |      |         |                | •     |

| V <sub>OL</sub>                                 | LOW level output voltage                                 | I <sub>O</sub> = 10 mA           | _    | _       | 0.3            | V     |

| I <sub>O(max)</sub>                             | maximum allowed output current                           |                                  | 10   | _       | _              | mA    |

| V <sub>O(max)</sub>                             | maximum allowed output voltage                           |                                  | _    | _       | V <sub>P</sub> | V     |

| $\delta_{df}$                                   | duty factor                                              | note 7                           | _    | 50      | _              | %     |

| FLYBACK INPU                                    | T/SANDCASTLE OUTPUT (PIN 38)                             | •                                |      |         |                | •     |

| I <sub>38</sub>                                 | required input current during flyback pulse              | note 7                           | 100  | -       | 300            | μΑ    |

| Vo                                              | output voltage during burst key                          |                                  | 4.8  | 5.3     | 5.8            | V     |

| Vo                                              | output voltage during blanking                           |                                  | 1.8  | 2.0     | 2.2            | V     |

| V <sub>Icl</sub>                                | clamped input voltage during flyback                     |                                  | 2.6  | 3.0     | 3.4            | V     |

| $t_{W}$                                         | burst key pulse width                                    |                                  | 3.3  | 3.5     | 3.7            | μs    |

| $t_{W}$                                         | vertical blanking pulse width                            | note 33                          | _    | 14      | _              | lines |

| $t_d$                                           | delay of start of burst key to start of sync             |                                  | 5.2  | 5.4     | 5.6            | μs    |

| VERTICAL SEC                                    | TION; NOTE 34                                            |                                  |      |         |                |       |

| f <sub>fr</sub>                                 | free running frequency                                   |                                  | _    | 50/60   | _              | Hz    |

| f <sub>lock</sub>                               | locking range                                            |                                  | 45   | _       | 64.5           | Hz    |

|                                                 | divider value not locked                                 |                                  | _    | 625/525 | _              |       |

|                                                 | locking range (lines/frame)                              |                                  | 488  | _       | 722            |       |

| VERTICAL RAM                                    | IP GENERATOR (PIN 42)                                    |                                  |      |         |                |       |

| I <sub>42</sub>                                 | input current during scan                                | note 7                           | _    | _       | 2              | μΑ    |

| I <sub>dis</sub>                                | discharge current during retrace                         |                                  | _    | 0.3     | _              | mA    |

| V <sub>saw(p-p)</sub>                           | sawtooth amplitude<br>(peak-to-peak value)               | in 50 Hz mode                    | _    | 1.5     | 1.8            | V     |

| t <sub>d</sub>                                  | delay from field-to-field                                |                                  | _    | _       | 1.6            | μs    |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL              | PARAMETER                                                                                  | CONDITIONS        | MIN.       | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------------------------------------------------------------|-------------------|------------|------|------|------|

| VERTICAL OUT        | TPUT (PIN 43)                                                                              |                   | <b>-</b> ' | ·    | -1   | '    |

| I <sub>O</sub>      | available output current                                                                   | note 7            | 1          | _    | _    | mA   |

| l <sub>int</sub>    | internal bias current of NPN emitter follower                                              |                   | -          | 0.2  | -    | mA   |

| V <sub>O(max)</sub> | maximum available output voltage                                                           |                   | 4          | _    | _    | V    |

| V <sub>O(min)</sub> | minimum available output voltage                                                           |                   | _          | _    | 0.3  | V    |

| VERTICAL FEE        | DBACK INPUT (PIN 41)                                                                       |                   |            |      |      |      |

| V <sub>41</sub>     | DC input voltage                                                                           |                   | 2.0        | 2.5  | 3.0  | V    |

| V <sub>41</sub>     | AC input voltage                                                                           |                   | _          | 1    | _    | V    |

| I <sub>41</sub>     | input current                                                                              |                   | _          | -    | 15   | μΑ   |

| $\Delta t_p$        | internal pre-correction to sawtooth                                                        | note 35           | _          | 3    | _    | %    |

| ΔΤ/ΔV               | temperature dependency on amplitude                                                        | ΔT = 40 °C        | _          | _    | 1    | %    |

| $V_{GL}$            | vertical guard switching level with respect to the DC feedback level; switching level LOW  |                   | -          | _    | -1.5 | V    |

| V <sub>GH</sub>     | vertical guard switching level with respect to the DC feedback level; switching level HIGH |                   | _          | _    | +1.5 | V    |

| t <sub>d</sub>      | delay of scan start                                                                        | power on at 60 Hz | _          | 140  | _    | ms   |

| Colour demo         | odulation part                                                                             |                   |            |      |      |      |

| CHROMINANCI         | E AMPLIFIER                                                                                |                   |            |      |      |      |

| ACC <sub>cr</sub>   | ACC control range                                                                          | note 36           | 26         | _    | _    | dB   |

| ΔV                  | change in amplitude of the output signals over the ACC range                               |                   | -          | -    | 2    | dB   |

| THR <sub>on</sub>   | threshold colour killer ON                                                                 |                   | -30        | _    | -38  | dB   |

| HYS <sub>off</sub>  | hysteresis colour killer OFF                                                               | note 7            |            |      |      |      |

|                     | strong input signal                                                                        | S/N ≥ 40 dB       | _          | +3   | _    | dB   |

|                     | noisy input signal                                                                         |                   | _          | +1   | _    | dB   |

| ACL CIRCUIT         |                                                                                            |                   |            |      |      |      |

|                     | chrominance burst ratio at which the ACL starts to operate                                 |                   | 2.3        | -    | 2.7  |      |

| REFERENCE P         | ART                                                                                        | •                 | -          |      | 1    | •    |

| Phase-locked        | d loop; note 37                                                                            |                   |            |      |      |      |

| f <sub>CR</sub>     | catching range                                                                             |                   | 300        | _    | _    | Hz   |

| Δφ                  | phase shift for a ±200 Hz deviation of the oscillator frequency                            | note 7            | _          | _    | 2    | deg  |

## Integrated PAL and PAL/NTSC TV processors

TDA8360; TDA8361; TDA8362

| SYMBOL                  | PARAMETER                                                                                                                                  | CONDITIONS                                               | MIN. | TYP.  | MAX. | UNIT |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|-------|------|------|

| Oscillator              |                                                                                                                                            |                                                          | !    |       | · !  | '    |

| TC <sub>osc</sub>       | temperature coefficient of fosc                                                                                                            | note 7                                                   | _    | 2.0   | 2.5  | Hz/K |

| $\Delta f_{OSC}$        | f <sub>osc</sub> deviation with respect to V <sub>P</sub>                                                                                  | note 7;<br>V <sub>P</sub> = 8 V ±10%                     | _    | -     | 250  | Hz   |

| R <sub>I</sub>          | input resistance (pin 34)                                                                                                                  | f <sub>i</sub> = 3.58 MHz; note 4                        | _    | 1.5   | _    | kΩ   |

| R <sub>I</sub>          | input resistance (pin 35)                                                                                                                  | f <sub>i</sub> = 4.43 MHz; note 4                        | _    | 1     | _    | kΩ   |

| C <sub>I</sub>          | input capacitance (pins 34 and 35)                                                                                                         | note 4                                                   | _    | _     | 10   | pF   |

| R                       | required resistance to V <sub>P</sub> to force the oscillator into one crystal mode                                                        |                                                          | _    | 47    | -    | kΩ   |

| HUE CONTROL             | AND CHROMINANCE OUTPUT (TDA8361, T                                                                                                         | DA8362); NOTE 38 (PIN 2                                  | 27)  |       |      |      |

| HUE <sub>cr</sub>       | hue control range                                                                                                                          | see also Fig.7                                           | ±45  | ±60   | _    | deg  |

| ΔHUE                    | hue variation for ±10% V <sub>P</sub>                                                                                                      | note 7                                                   | _    | 0     | 5    | deg  |

| ΔΗUΕ/ΔΤ                 | hue variation with temperature                                                                                                             | $T_{amb} = 0 \text{ to } +7 ^{\circ}\text{C};$<br>note 7 | _    | 0     | _    | deg  |

| R                       | value of resistor connected to V <sub>P</sub> to switch the PAL decoder and to obtain a chrominance input signal for the TDA8395 (TDA8362) |                                                          | 4.7  | 10    | 12   | kΩ   |

| $V_{O(p-p)}$            | chrominance output signal to the TDA8395 (peak-to-peak value)                                                                              | nominal output signal                                    | _    | 330   | _    | mV   |

| DEMODULATOR             | RS                                                                                                                                         |                                                          | •    | •     | •    | •    |

| V <sub>30(p-p)</sub>    | (R–Y) output signal amplitude (peak-to-peak value)                                                                                         | note 39                                                  | _    | 0.525 | _    | V    |

| V <sub>31(p-p)</sub>    | (B–Y) output signal amplitude (peak-to-peak value)                                                                                         | note 39                                                  | _    | 0.675 | _    | V    |

| G                       | gain ratio of both demodulators G(B–Y)/G(R–Y)                                                                                              |                                                          | 1.6  | 1.78  | 1.96 |      |