### SPS

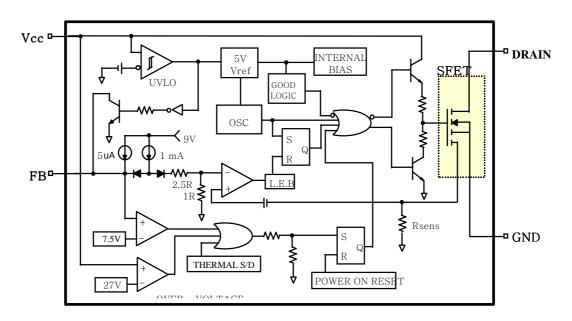

The SPS product family is specially designed for an off-line SMPS with minimal external components. The SPS consist of high voltage power SenseFET and current mode PWM IC.

Included PWM controller features integrated fixed oscillator, under voltage lock out, leading edge blanking, optimized gate turn-on/turn-off driver, thermal shut down protection, over voltage protection, and temperature compensated precision current sources for loop compensation and fault protection circuitry. Compared to discrete MOSFET and controller or RCC switching converter solution, a SPS can reduce total component count, design size, weight and at the same time increase efficiency, productivity, and system reliability. It has a basic platform well suited for cost-effective design in either a flyback converter or a forward converter.

#### **FEATURES**

- Precision fixed operating frequency (67kHz)

- Pulse by pulse current limiting

- Over current protection

- Over voltage protection (Min. 25V)

- Internal thermal shutdown function

- Under voltage lockout

- Internal high voltage sense FET

- Auto-restart mode

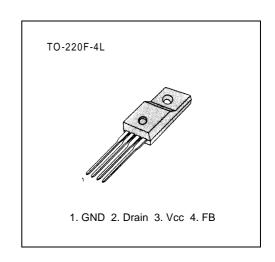

#### ORDERING INFORMATION

| Device    | Package    | Topr (°C)      |

|-----------|------------|----------------|

| KA5M0165R | TO-220F-4L | −25°C to +85°C |

### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                                   | Symbol                  | Value                   | Unit            |

|--------------------------------------------------|-------------------------|-------------------------|-----------------|

| Drain-source (GND) voltage (1)                   | $V_{DSS}$               | 650                     | V               |

| Drain-Gate voltage ( $R_{GS}$ =1 $M\Omega$ )     | $V_{DGR}$               | 650                     | V               |

| Gate-source (GND) voltage                        | $V_{GS}$                | ±30                     | V               |

| Drain current pulsed (2)                         | I <sub>DM</sub>         | 4.0                     | A <sub>DC</sub> |

| Single pulsed avalanche energy (3)               | E <sub>AS</sub>         | 95                      | mJ              |

| Avalanche current (4)                            | I <sub>AS</sub>         | 5                       | A               |

| Continuous drain current (T <sub>C</sub> =25°C)  | I <sub>D</sub>          | 1.0                     | A <sub>DC</sub> |

| Continuous drain current (T <sub>C</sub> =100°C) | I <sub>D</sub>          | 0.7                     | A <sub>DC</sub> |

| Supply voltage                                   | V <sub>CC</sub>         | 30                      | V               |

| Analog input voltage range                       | V <sub>FB</sub>         | −0.3 to V <sub>SD</sub> | V               |

| Total power dissipation                          | P <sub>D</sub> (wt H/S) | 40                      | W               |

|                                                  | Derating                | 0.32                    | W/°C            |

| Operating temperature                            | T <sub>OPR</sub>        | -25 to +85              | °C              |

| Storage temperature                              | T <sub>STG</sub>        | -55 to +150             | °C              |

#### NOTES:

- 1. Tj=25°C to 150°C

- 2. Repetitive rating: Pulse width limited by maximum junction temperature

- 3. L=24mH, starting Tj=25°C

- 4. L=13uH, starting Tj=25°C

# **ELECTRICAL CHARACTERISTICS (SFET part)**

(Ta=25°C unless otherwise specified)

| Characteristic                             | Symbol              | Test condition                                                                                                                                                             | Min. | Тур. | Max. | Unit |

|--------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Drain-source breakdown voltage             | BV <sub>DSS</sub>   | $V_{GS}$ =0V, $I_D$ =50 $\mu$ A                                                                                                                                            | 650  | _    | _    | V    |

| Zero gate voltage drain current            | I <sub>DSS</sub>    | V <sub>DS</sub> =Max., Rating, V <sub>GS</sub> =0V                                                                                                                         | _    | _    | 50   | μΑ   |

|                                            |                     | V <sub>DS</sub> =0.8Max., Rating,<br>V <sub>GS</sub> =0V, T <sub>C</sub> =125°C                                                                                            | _    | _    | 200  | μА   |

| Static drain-source on resistance (note)   | R <sub>DS(ON)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =0.5A                                                                                                                                 | _    | 8    | 10   | Ω    |

| Forward transconductance (note)            | gfs                 | V <sub>DS</sub> =50V, I <sub>D</sub> =0.5A                                                                                                                                 | 0.5  | _    | _    | S    |

| Input capacitance                          | Ciss                | V <sub>GS</sub> =0V, V <sub>DS</sub> =25V,<br>f=1MHz                                                                                                                       | _    | 250  | _    | pF   |

| Output capacitance                         | Coss                |                                                                                                                                                                            | _    | 25   | _    |      |

| Reverse transfer capacitance               | Crss                |                                                                                                                                                                            | _    | 10   | _    |      |

| Turn on delay time                         | td(on)              | V <sub>DD</sub> =0.5BV <sub>DSS</sub> , I <sub>D</sub> =1.0A<br>(MOSFET switching<br>time are essentially<br>independent of<br>operating temperature)                      | _    | 12   | _    | nS   |

| Rise time                                  | tr                  |                                                                                                                                                                            | _    | 4    | _    |      |

| Turn off delay time                        | td(off)             |                                                                                                                                                                            | _    | 30   | _    |      |

| Fall time                                  | tf                  |                                                                                                                                                                            | _    | 10   | _    |      |

| Total gate charge (gate-source+gate-drain) | Qg                  | V <sub>GS</sub> =10V, I <sub>D</sub> =1.0A,<br>V <sub>DS</sub> =0.5BV <sub>DSS</sub> (MOSFET<br>switching time are<br>essentially independent of<br>operating temperature) | _    | _    | 21   | nC   |

| Gate-source charge                         | Qgs                 |                                                                                                                                                                            | _    | 3    | _    |      |

| Gate-drain (Miller) charge                 | Qgd                 |                                                                                                                                                                            | _    | 9    | _    |      |

**NOTE:** Pulse test: Pulse width  $\leq 300\mu S$ , duty cycle  $\leq 2\%$

# **ELECTRICAL CHARACTERISTICS (Control part)**

(Ta=25°C unless otherwise specified)

| Characteristic                               | Symbol               | Test condition                             | Min. | Тур. | Max. | Unit  |  |

|----------------------------------------------|----------------------|--------------------------------------------|------|------|------|-------|--|

| REFERENCE SECTION                            |                      |                                            |      |      |      |       |  |

| Output voltage (1)                           | Vref                 | Ta=25°C                                    | 4.80 | 5.00 | 5.20 | V     |  |

| Temperature Stability (1)(2)                 | Vref/∆T              | –25°C≤Ta≤+85°C                             | -    | 0.3  | 0.6  | mV/°C |  |

| OSCILLATOR SECTION                           |                      |                                            |      |      |      |       |  |

| Initial accuracy                             | Fosc                 | Ta=25°C                                    | 61   | 67   | 73   | kHz   |  |

| Frequency change with temperature (2)        | ΔF/ΔΤ                | –25°C≤Ta≤+85°C                             | -    | ±5   | ±10  | %     |  |

| PWM SECTION                                  |                      |                                            |      |      |      |       |  |

| Maximum duty cycle                           | Dmax                 | _                                          | 74   | 77   | 80   | %     |  |

| FEEDBACK SECTION                             |                      |                                            |      |      |      |       |  |

| Feedback source current                      | I <sub>FB</sub>      | Ta=25°C, 0V <u>&lt;</u> Vfb <u>&lt;</u> 3V | 0.7  | 0.9  | 1.1  | mA    |  |

| Shutdown delay current                       | Idelay               | Ta=25°C, 5V≤Vfb≤V <sub>SD</sub>            | 4    | 5    | 6    | μΑ    |  |

| OVER CURRENT PROTECTION SECTION              |                      |                                            |      |      |      |       |  |

| Over current protection                      | I <sub>L</sub> (max) | Max. inductor current                      | 0.53 | 0.6  | 0.67 | Α     |  |

| UVLO SECTION                                 |                      |                                            |      |      |      |       |  |

| Start threshold voltage                      | Vth(H)               | -                                          | 14   | 15   | 16   | V     |  |

| Minimum operating voltage                    | Vth(L)               | After turn on                              | 8.4  | 9    | 9.6  | V     |  |

| TOTAL STANDBY CURRENT SECTION                | N                    |                                            |      |      |      |       |  |

| Start current                                | I <sub>ST</sub>      | V <sub>CC</sub> =14V                       | _    | 100  | 170  | mA    |  |

| Operating supply current (control part only) | I <sub>OPR</sub>     | V <sub>CC</sub> ≤28                        | _    | 7    | 12   | mA    |  |

| SHUTDOWN SECTION                             |                      |                                            | 1    | •    |      |       |  |

| Shutdown Feedback voltage                    | V <sub>SD</sub>      | Vfb <u>&gt;</u> 6.5V                       | 6.9  | 7.5  | 8.1  | V     |  |

| Thermal shutdown temperature (Tj) (1)        | T <sub>SD</sub>      | -                                          | 140  | 160  | _    | °C    |  |

| Over voltage protection                      | V <sub>OVP</sub>     | V <sub>CC≥</sub> 24V                       | 25   | 27   | 29   | V     |  |

## NOTES:

- 1. These parameters, although guaranteed, are not 100% tested in production

- 2. These parameters, although guaranteed, are tested in EDS (wafer test) process

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www fairchildsemi com