# JPEG2000 Video Codec

**ADV212**

#### **FEATURES**

Complete single-chip JPEG2000 compression and decompression solution for video and still images Identical in pinout and footprint to the ADV202 and supports all the functionality of the ADV202

Power reduction of at least 30% compared with ADV202 JTAG/boundary scan support

Patented SURF (spatial ultraefficient recursive filtering) technology enables low power, low cost wavelet-based compression

Supports both 9/7 and 5/3 wavelet transforms with up to 6 levels of transform

Video interface directly supporting ITU-R BT.656, SMPTE 125M PAL/NTSC, SMPTE 274M, SMPTE 293M (525p), and ITU-R BT.1358 (625p) or any video format with a maximum input rate of 65 MSPS for irreversible mode or 40 MSPS for reversible mode

Programmable tile/image size with widths up to 4096 pixels in single-component mode; maximum tile/image height: 4096 pixels

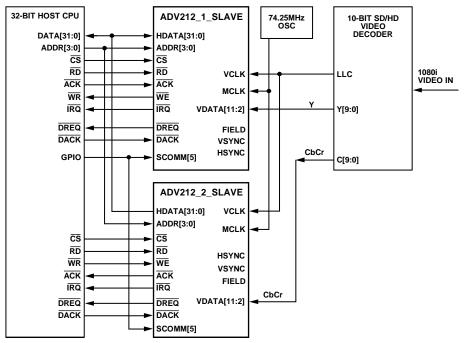

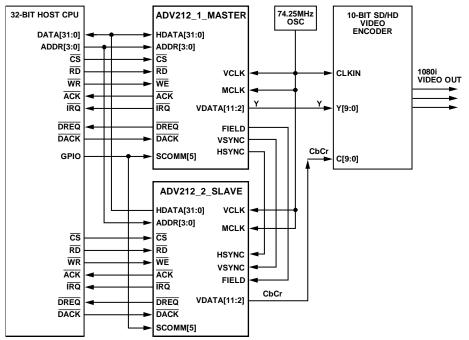

2 or more ADV212s can be combined to support full-frame SMPTE 274M HDTV (1080i) or SMPTE 296M (720p)

Flexible, asynchronous SRAM-style host interface allows glueless connection to most 16-/32-bit microcontrollers and ASICs

2.5 V or 3.3 V input/output and 1.5 V core supply

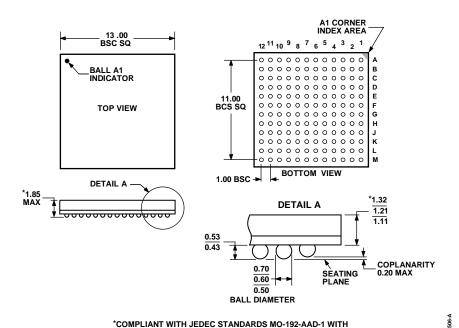

12 mm × 12 mm, 121-ball CSP\_BGA with a speed grade of

115 MHz or 13 mm × 13 mm, 144-ball CSP\_BGA with a

speed grade of 150 MHz

#### **APPLICATIONS**

Networked video and image distribution systems

Wireless video and image distribution

Image archival/retrieval

Digital CCTV and surveillance systems

Digital cinema systems

Professional video editing and recording

Digital still cameras

Digital camcorders

#### **GENERAL DESCRIPTION**

The ADV212 is a single-chip JPEG2000 codec targeted for video and high bandwidth image compression applications that can benefit from the enhanced quality and features provided by the JPEG2000 (J2K) ISO/IEC15444-1 image compression standard. The part implements the computationally intensive operations of the JPEG2000 image compression standard and provides fully compliant code-stream generation for most applications.

The dedicated video port of the ADV212 provides glueless connection to common digital video standards such as ITU-R BT.656, SMPTE 125M, SMPTE 293M (525p), ITU-R BT.1358 (625p), SMPTE 274M (1080i), or SMPTE 296M (720p). A variety of other high speed, synchronous pixel and video formats can also be supported by using the programmable framing and validation signals.

The ADV212 is an upgrade version of the ADV202 that is identical in pinout and footprint. It supports all the functionality of the ADV202 and has the following additional options: JTAG/boundary scan support and power reduction of at least 30% compared with the ADV202.

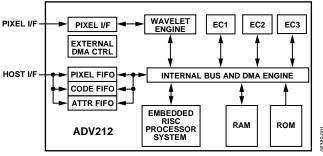

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                           |

|----------------------------------------------------|

| Applications1                                      |

| General Description                                |

| Functional Block Diagram1                          |

| Revision History2                                  |

| JPEG2000 Feature Support3                          |

| Specifications4                                    |

| Supply Voltages and Current4                       |

| Input/Output Specifications4                       |

| Clock and RESET Specifications                     |

| Normal Host Mode—Write Operation 6                 |

| Normal Host Mode—Read Operation                    |

| DREQ/DACK DMA Mode—Single FIFO Write Operation 8   |

| DREQ/DACK DMA Mode—Single FIFO Read Operation . 10 |

| External DMA Mode—FIFO Write, Burst Mode12         |

| External DMA Mode—FIFO Read, Burst Mode            |

| Streaming Mode (JDATA)—FIFO Read/Write14           |

| VDATA Mode Timing                                  |

| Raw Pixel Mode Timing17                            |

| JTAG Timing18                                      |

| Absolute Maximum Ratings                           |

| Thermal Resistance                                 |

| ESD Caution                                        |

| Pin Configurations and Function Descriptions       |

| Theory of Operation                                |

| Wavelet Engine                                     |

| Entropy Codecs                                     |

| Embedded Processor System                          |

| REVISION HISTORY                                   |

| 4/08—Rev. 0 to Rev. A                              |

| Change to Table 1, Static Current Parameter 4      |

| Memory System25                       |

|---------------------------------------|

| Internal DMA Engine                   |

| ADV212 Interfaces                     |

| Video Interface (VDATA Bus)26         |

| Host Interface (HDATA Bus)            |

| Direct and Indirect Registers         |

| Control Access Registers              |

| Pin Configuration and Bus Sizes/Modes |

| Stage Register                        |

| JDATA Mode27                          |

| External DMA Engine                   |

| Internal Registers                    |

| Direct Registers                      |

| Indirect Registers                    |

| PLL Registers                         |

| Hardware Boot Modes31                 |

| Video Input Formats                   |

| Applications Information              |

| Encode—Multichip Mode                 |

| Decode—Multichip Master/Slave         |

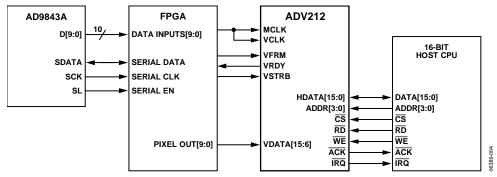

| Digital Still Camera/Camcorder        |

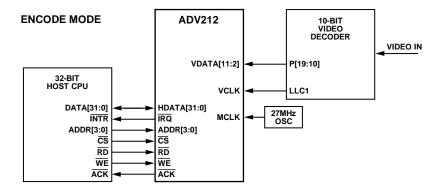

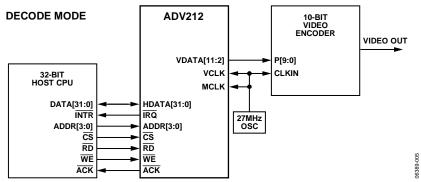

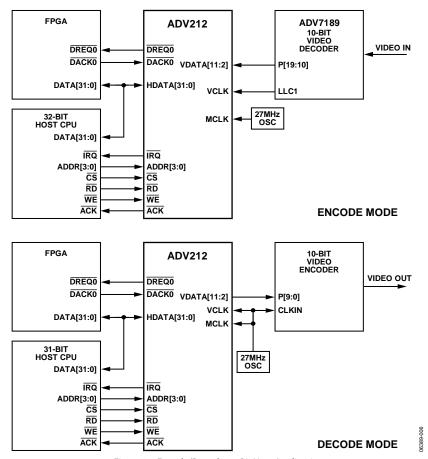

| Encode/Decode SDTV Video Application  |

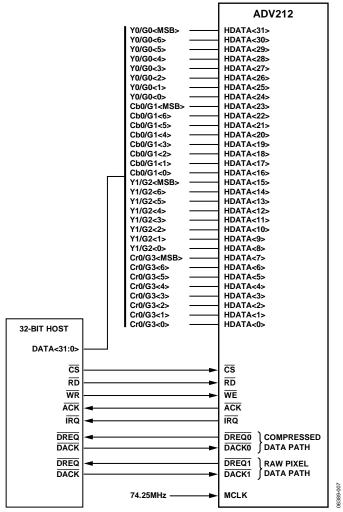

| 32-Bit Host Application               |

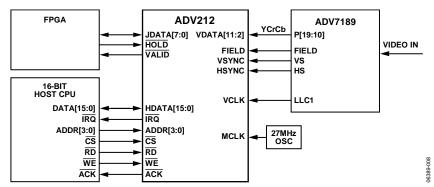

| HIPI (Host Interface—Pixel Interface) |

| JDATA Interface                       |

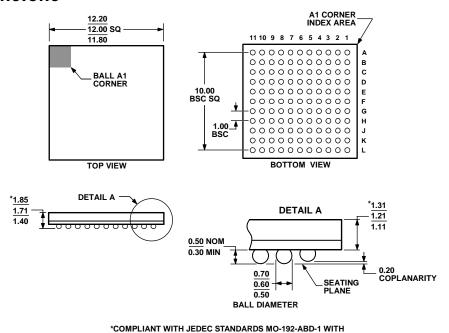

| Outline Dimensions                    |

| Ordering Guide42                      |

The ADV212 can process images at a rate of 40 MSPS in reversible mode and at higher rates when used in irreversible mode. The ADV212 contains a dedicated wavelet transform engine, three entropy codecs, an on-board memory system, and an embedded reduced instruction set computer (RISC) processor that can provide a complete JPEG2000 compression/decompression solution.

The wavelet processor supports the 9/7 irreversible wavelet transform and the 5/3 wavelet transform in reversible and irreversible modes. The entropy codecs support all features in the JPEG2000 Part 1 specification, except maximum shift region of interest (ROI).

The ADV212 operates on a rectangular array of pixel samples called a tile. A tile can contain a complete image, up to the maximum supported size, or some portion of an image. The maximum horizontal tile size supported depends on the wavelet transform selected and the number of samples in the tile. Images larger than the ADV212 maximum tile size can be broken into individual tiles and then sent sequentially to the chip while maintaining a single, fully compliant JPEG2000 code stream for the entire image.

#### JPEG2000 FEATURE SUPPORT

The ADV212 supports a broad set of features that are included in Part 1 of the JPEG2000 standard (ISO/IEC 15444).

Depending on the particular application requirements, the ADV212 can provide varying levels of JPEG2000 compression support. It can provide raw code block and attribute data output, which allows the host software to have complete control over the generation of the JPEG2000 code stream and other aspects of the compression process such as bit-rate control. Additionally, the ADV212 can create a complete, fully compliant JPEG2000 code stream (J2C) and enhanced file formats such as JP2.

# **SPECIFICATIONS**

Specifications apply to IOVDD = 2.5 V or 3.3 V over the operating temperature range, unless otherwise specified.

#### **SUPPLY VOLTAGES AND CURRENT**

Table 1.

| Parameter                                                     | Mnemonic        | Min   | Тур | Max               | Unit |

|---------------------------------------------------------------|-----------------|-------|-----|-------------------|------|

| DC Supply Voltage, Core                                       | VDD             | 1.425 | 1.5 | 1.575             | V    |

| DC Supply Voltage, Input/Output                               | IOVDD           | 2.375 | 2.5 | 2.625             | V    |

|                                                               | IOVDD           | 3.135 | 3.3 | 3.465             | V    |

| Input Range                                                   | $V_{IN}$        | -0.3  |     | $V_{DDI/O} + 0.3$ | V    |

| Operating Ambient Temperature Range in Free Air               | Т               | -40   | +25 | +85               | °C   |

| Static Current <sup>1</sup>                                   | I <sub>DD</sub> |       | 60  |                   | mA   |

| Dynamic Current, Core (JCLK Frequency = 150 MHz) <sup>2</sup> |                 |       | 380 | 440               | mA   |

| Dynamic Current, Core (JCLK Frequency = 108 MHz)              |                 |       | 280 | 320               | mA   |

| Dynamic Current, Core (JCLK Frequency = 81 MHz)               |                 |       | 210 | 290               | mA   |

| Dynamic Current, Input/Output                                 |                 |       | 40  | 50                | mA   |

<sup>&</sup>lt;sup>1</sup> No clock or input/output activity. <sup>2</sup> ADV212-150 only.

#### **INPUT/OUTPUT SPECIFICATIONS**

Table 2.

| Parameter                              | Mnemonic                       | Min | Тур | Max | Unit | Test Conditions                           |

|----------------------------------------|--------------------------------|-----|-----|-----|------|-------------------------------------------|

| High Level Input Voltage               | V <sub>IH</sub> (3.3 V)        | 2.2 |     |     | ٧    | VDD = maximum                             |

|                                        | V <sub>IH (2.5 V)</sub>        | 1.9 |     |     | V    | VDD = maximum                             |

| Low Level Input Voltage                | V <sub>IL</sub> (3.3 V, 2.5 V) |     |     | 0.6 | V    | VDD = minimum                             |

| High Level Output Voltage              | V <sub>OH (3.3 V)</sub>        | 2.4 |     |     | V    | $VDD = minimum, I_{OH} = -0.5 mA$         |

|                                        | <b>V</b> OH (2.5 V)            | 2.0 |     |     | V    | VDD = minimum, $I_{OH} = -0.5 \text{ mA}$ |

| Low Level Output Voltage               | V <sub>OL (3.3 V, 2.5 V)</sub> |     |     | 0.4 | V    | $VDD = minimum, I_{OL} = +2 mA$           |

| High Level Input Current               | Iн                             |     |     | 1.0 | μΑ   | $VDD = maximum, V_{IN} = VDD$             |

| Low Level Input Current                | I <sub>IL</sub>                |     |     | 1.0 | μΑ   | $VDD = maximum, V_{IN} = 0 V$             |

| High Level Three-State Leakage Current | l <sub>ozh</sub>               |     |     | 1.0 | μΑ   | $VDD = maximum, V_{IN} = VDD$             |

| Low Level Three-State Leakage Current  | lozL                           |     |     | 1.0 | μΑ   | $VDD = maximum, V_{IN} = 0 V$             |

| Input Pin Capacitance                  | Cı                             |     |     | 8   | рF   |                                           |

| Output Pin Capacitance                 | Co                             |     |     | 8   | pF   |                                           |

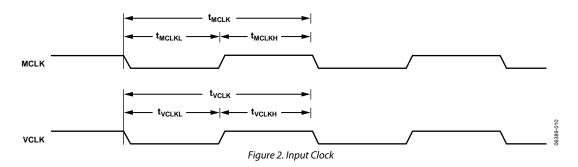

## **CLOCK AND RESET SPECIFICATIONS**

Table 3.

| Parameter       | Mnemonic           | Min  | Тур | Max   | Unit                     |

|-----------------|--------------------|------|-----|-------|--------------------------|

| MCLK Period     | t <sub>MCLK</sub>  | 13.3 |     | 100   | ns                       |

| MCLK Frequency  | f <sub>MCLK</sub>  | 10   |     | 75.18 | MHz                      |

| MCLK Width Low  | t <sub>MCLKL</sub> | 6    |     |       | ns                       |

| MCLK Width High | t <sub>MCLKH</sub> | 6    |     |       | ns                       |

| VCLK Period     | t <sub>VCLK</sub>  | 13.4 |     | 50    | ns                       |

| VCLK Frequency  | f <sub>VCLK</sub>  | 20   |     | 74.60 | MHz                      |

| VCLK Width Low  | t <sub>VCLKL</sub> | 5    |     |       | ns                       |

| VCLK Width High | tvclkh             | 5    |     |       | ns                       |

| RESET Width Low | t <sub>RESET</sub> | 5    |     |       | MCLK cycles <sup>1</sup> |

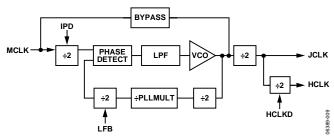

$<sup>^{\</sup>rm 1}$  For a definition of MCLK, see Figure 32.

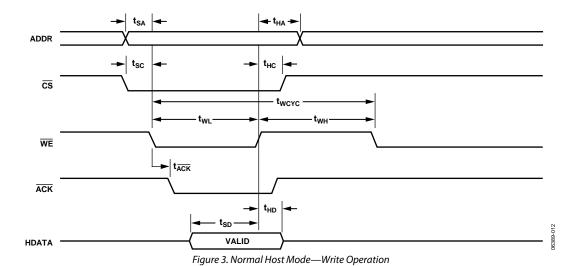

## NORMAL HOST MODE—WRITE OPERATION

Table 4.

| Parameter                                                     | Mnemonic                        | Min 1                 | Гур | Max                         | Unit |

|---------------------------------------------------------------|---------------------------------|-----------------------|-----|-----------------------------|------|

| WE to ACK, Direct Registers and FIFO Accesses                 | t <sub>ACK</sub> (direct)       | 5                     |     | $1.5 \times JCLK + 7.0^{1}$ | ns   |

| WE to ACK, Indirect Registers                                 | $t_{\overline{ACK}}$ (indirect) | 5                     |     | $2.5\times JCLK + 7.0^{1}$  | ns   |

| Data Setup                                                    | t <sub>SD</sub>                 | 3.0                   |     |                             | ns   |

| Data Hold                                                     | t <sub>HD</sub>                 | 1.5                   |     |                             | ns   |

| Address Setup                                                 | t <sub>SA</sub>                 | 2                     |     |                             | ns   |

| Address Hold                                                  | t <sub>HA</sub>                 | 2                     |     |                             | ns   |

| CS to WE Setup                                                | t <sub>SC</sub>                 | 0                     |     |                             | ns   |

| CS Hold                                                       | t <sub>HC</sub>                 | 0                     |     |                             | ns   |

| Write Inactive Pulse Width (Minimum Time Until Next WE Pulse) | t <sub>wh</sub>                 | 2.5 JCLK <sup>1</sup> |     |                             | ns   |

| Write Active Pulse Width                                      | t <sub>WL</sub>                 | 2.5 JCLK <sup>1</sup> |     |                             | ns   |

| Write Cycle Time                                              | twcyc                           | 5 JCLK <sup>1</sup>   |     |                             | ns   |

$<sup>^{\</sup>rm 1}$  For a definition of JCLK, see Figure 32.

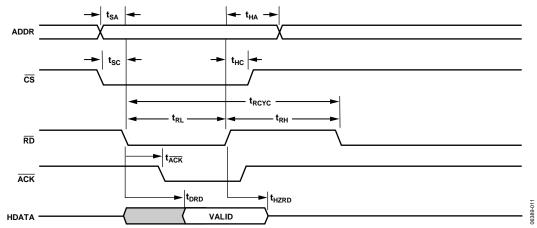

### **NORMAL HOST MODE—READ OPERATION**

Table 5.

| Parameter                                     | Mnemonic                                 | Min                    | Тур | Max                          | Unit |

|-----------------------------------------------|------------------------------------------|------------------------|-----|------------------------------|------|

| RD to ACK, Direct Registers and FIFO Accesses | t <sub>ACK</sub> (direct) <sup>1</sup>   | 5                      |     | $1.5 \times JCLK + 7.0^{2}$  | ns   |

| RD to ACK, Indirect Registers                 | t <sub>ACK</sub> (indirect) <sup>1</sup> | 10.5 JCLK <sup>2</sup> |     | $15.5 \times JCLK + 7.0^{2}$ | ns   |

| Read Access Time, Direct Registers            | t <sub>DRD</sub> (direct)                | 5                      |     | $1.5 \times JCLK + 7.0^{2}$  | ns   |

| Read Access Time, Indirect Registers          | t <sub>DRD</sub> (indirect)              | 10.5 JCLK <sup>2</sup> |     | $15.5 \times JCLK + 7.0^{2}$ | ns   |

| Data Hold                                     | t <sub>HZRD</sub>                        | 2                      |     | 8.5                          | ns   |

| CS to RD Setup                                | t <sub>sc</sub>                          | 0                      |     |                              | ns   |

| Address Setup                                 | t <sub>SA</sub>                          | 2                      |     |                              | ns   |

| CS Hold                                       | t <sub>HC</sub>                          | 0                      |     |                              | ns   |

| Address Hold                                  | t <sub>HA</sub>                          | 2                      |     |                              | ns   |

| Read Inactive Pulse Width                     | t <sub>RH</sub>                          | 2.5 JCLK <sup>2</sup>  |     |                              | ns   |

| Read Active Pulse Width                       | t <sub>RL</sub>                          | 2.5 JCLK <sup>2</sup>  |     |                              | ns   |

| Read Cycle Time, Direct Registers             | t <sub>RCYC</sub>                        | 5.0 JCLK <sup>2</sup>  |     |                              | ns   |

<sup>&</sup>lt;sup>1</sup> Timing relationship between  $\overline{ACK}$  falling transition and HDATA valid is not guaranteed. HDATA valid hold time is guaranteed with respect to  $\overline{RD}$  rising transition. A minimum of three JCLK cycles is recommended between  $\overline{ACK}$  assert and  $\overline{RD}$  deassert.

<sup>2</sup> For a definition of JCLK, see Figure 32.

Figure 4. Normal Host Mode—Read Operation

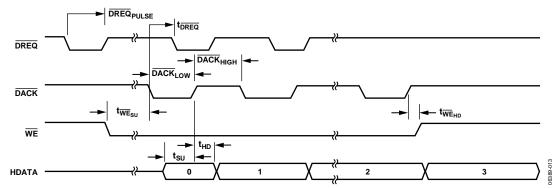

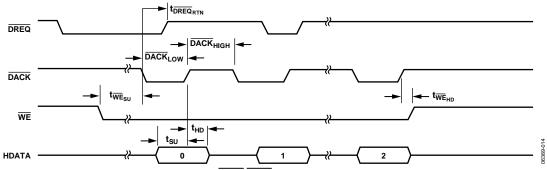

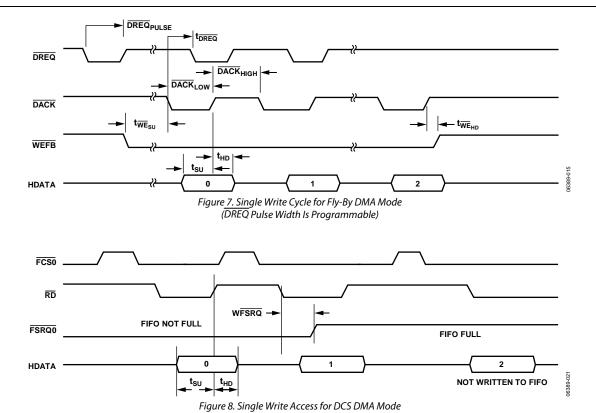

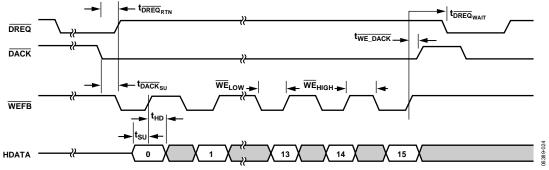

## **DREQ/DACK DMA MODE—SINGLE FIFO WRITE OPERATION**

Table 6.

| Parameter                                                                     | Mnemonic                 | Min                   | Тур | Max                         | Unit |

|-------------------------------------------------------------------------------|--------------------------|-----------------------|-----|-----------------------------|------|

| DREQ Pulse Width                                                              | DREQ <sub>PULSE</sub>    | 1 JCLK <sup>1</sup>   |     | 15 JCLK <sup>1</sup>        | ns   |

| DACK Assert to Subsequent DREQ Delay                                          | t <sub>DREQ</sub>        | 2.5 JCLK <sup>1</sup> |     | $3.5 \times JCLK + 8.5^{1}$ | ns   |

| WE to DACK Setup                                                              | $t_{\overline{WE}_{SU}}$ | 0                     |     |                             | ns   |

| Data to DACK Deassert Setup                                                   | t <sub>su</sub>          | 2                     |     |                             | ns   |

| Data to DACK Deassert Hold                                                    | t <sub>HD</sub>          | 2                     |     |                             | ns   |

| DACK Assert Pulse Width                                                       | DACK <sub>LOW</sub>      | 2 JCLK <sup>1</sup>   |     |                             | ns   |

| DACK Deassert Pulse Width                                                     | DACK                     | 2 JCLK <sup>1</sup>   |     |                             | ns   |

| WE Hold After DACK Deassert                                                   | $t_{\overline{WE}_{HD}}$ | 0                     |     |                             | ns   |

| WE Assert to FSRQ Deassert (FIFO Full)                                        | WFSRQ                    | 1.5 JCLK <sup>1</sup> |     | $2.5 \times JCLK + 7.5^{1}$ | ns   |

| $\overline{\text{DACK}}$ to $\overline{\text{DREQ}}$ Deassert (DR × PULS = 0) | t <sub>DREQRTN</sub>     | 2.5 JCLK <sup>1</sup> |     | $3.5 \times JCLK + 9.0^{1}$ | ns   |

$<sup>^{\</sup>rm 1}$  For a definition of JCLK, see Figure 32.

Figure 5. Single Write for DREQ/DACK DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:1] Not Programmed to a Value of 0000)

Figure 6. Single Write for DREO/DACK DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:11] Programmed to a Value of 0000)

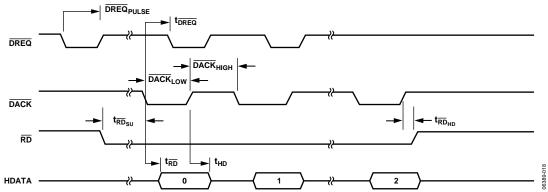

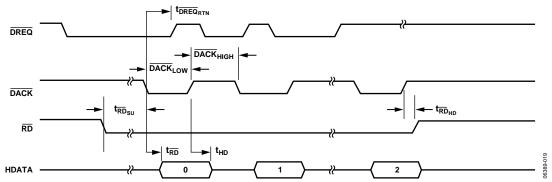

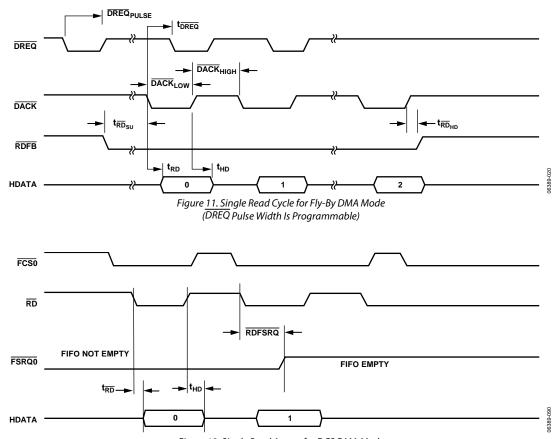

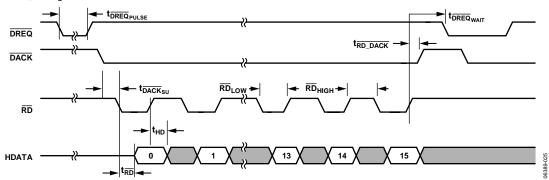

## **DREQ/DACK DMA MODE—SINGLE FIFO READ OPERATION**

Table 7.

| Parameter                                                       | Mnemonic                    | Min                   | Тур | Max                         | Unit |

|-----------------------------------------------------------------|-----------------------------|-----------------------|-----|-----------------------------|------|

| DREQ Pulse Width                                                | DREQ <sub>PULSE</sub>       | 1 JCLK <sup>1</sup>   |     | 15 JCLK <sup>1</sup>        | ns   |

| DACK Assert to Subsequent DREQ Delay                            | t <sub>DREQ</sub>           | 2.5 JCLK <sup>1</sup> |     | $3.5 \times JCLK + 9.0^{1}$ | ns   |

| RD to DACK Setup                                                | t <sub>RDSU</sub>           | 0                     |     |                             | ns   |

| DACK to Data Valid                                              | t <sub>RD</sub>             | 2.5                   |     | 11                          | ns   |

| Data Hold                                                       | t <sub>HD</sub>             | 1.5                   |     |                             | ns   |

| DACK Assert Pulse Width                                         | DACKLOW                     | 2 JCLK <sup>1</sup>   |     |                             | ns   |

| DACK Deassert Pulse Width                                       | DACK <sub>HIGH</sub>        | 2 JCLK <sup>1</sup>   |     |                             | ns   |

| RD Hold after DACK Deassert                                     | $t_{\overline{RD}_{HD}}$    | 0                     |     |                             | ns   |

| RD Assert to FSRQ Deassert (FIFO Empty)                         | RDFSRQ                      | 1.5 JCLK <sup>1</sup> |     | $2.5 \times JCLK + 9.0^{1}$ | ns   |

| $\overline{DACK}$ to $\overline{DREQ}$ Deassert (DR × PULS = 0) | $t_{\overline{DREQ}_{RTN}}$ | 2.5 JCLK <sup>1</sup> |     | $3.5 \times JCLK + 9.0^{1}$ | ns   |

<sup>&</sup>lt;sup>1</sup> For a definition of JCLK, see Figure 32.

Figure 9. Single Read for DREQ/DACK DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:11] Not Programmed to a Value of 0000)

Figure 10. Single Read for DREQ/DACK DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:11] Programmed to a Value of 0000)

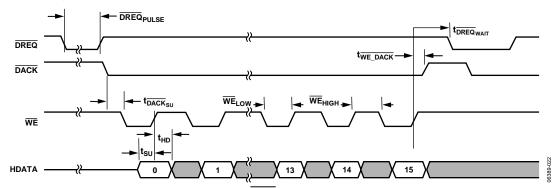

## **EXTERNAL DMA MODE—FIFO WRITE, BURST MODE**

Table 8.

| Parameter                                                                   | Mnemonic                    | Min T                 | ур | Max                       | Unit |

|-----------------------------------------------------------------------------|-----------------------------|-----------------------|----|---------------------------|------|

| DREQ Pulse Width <sup>1</sup>                                               | DREQ <sub>PULSE</sub>       | 1 JCLK <sup>2</sup>   |    | 15 JCLK <sup>2</sup>      | ns   |

| $\overline{\text{WE}}$ to $\overline{\text{DREQ}}$ Deassert (DR × PULS = 0) | $t_{\overline{DREQ}_{RTN}}$ | 2.5 JCLK <sup>2</sup> |    | $3.5 \times JCLK + 7.5^2$ | ns   |

| DACK to WE Setup                                                            | t <sub>DACK</sub> SU        | 0                     |    |                           | ns   |

| Data Setup                                                                  | t <sub>SU</sub>             | 2.5                   |    |                           | ns   |

| Data Hold                                                                   | t <sub>HD</sub>             | 2                     |    |                           | ns   |

| WE Assert Pulse Width                                                       | WELOW                       | 1.5 JCLK <sup>2</sup> |    |                           | ns   |

| WE Deassert Pulse Width                                                     | WE <sub>HIGH</sub>          | 1.5 JCLK <sup>2</sup> |    |                           | ns   |

| WE Deassert to Next DREQ                                                    | t <sub>DREQWAIT</sub>       | 2.5 JCLK <sup>2</sup> |    | $4.5 \times JCLK + 9.0^2$ | ns   |

| WE Deassert to DACK Deassert                                                | t <sub>WE_DACK</sub>        | 0                     |    |                           | ns   |

$<sup>^{\</sup>rm 1}$  Applies to assigned DMA channel, if EDMOD0/EDMOD1[14:11] is programmed to a nonzero value.  $^{\rm 2}$  For a definition of JCLK, see Figure 32.

Figure 13. Burst Write Cycle for DREQ/DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:1] Not Programmed to a Value of 0000)

Figure 14. Burst Write Cycle for DREQ/DMA Mode for Assigned DMA Channel (EDMOD0/EDMOD1[14:11] Programmed to a Value of 0000)

Figure 15. Burst Write Cycle for Fly-By DMA Mode

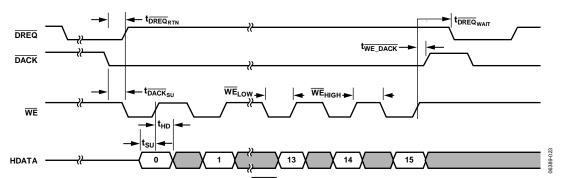

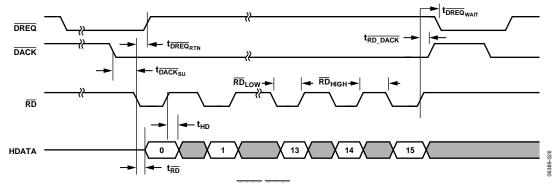

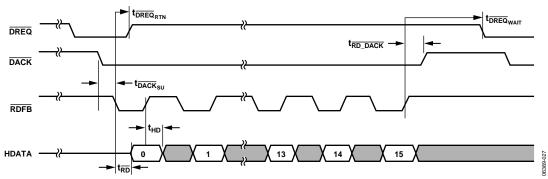

#### **EXTERNAL DMA MODE—FIFO READ, BURST MODE**

Table 9.

| Parameter                                                     | Mnemonic               | Min                   | Тур | Max                       | Unit |

|---------------------------------------------------------------|------------------------|-----------------------|-----|---------------------------|------|

| DREQ Pulse Width <sup>1</sup>                                 | DREQ <sub>PULSE</sub>  | 1 JCLK <sup>2</sup>   |     | 15 JCLK <sup>2</sup>      | ns   |

| $\overline{RD}$ to $\overline{DREQ}$ Deassert (DR × PULS = 0) | t <sub>DREQRTN</sub>   | 2.5 JCLK <sup>2</sup> |     | $3.5 \times JCLK + 7.5^2$ | ns   |

| DACK to RD Setup                                              | t <sub>DACK</sub> SU   | 0                     |     |                           | ns   |

| RD to Data Valid                                              | t <sub>RD</sub>        | 2.5                   |     | 9.7                       | ns   |

| Data Hold                                                     | t <sub>HD</sub>        | 2.5                   |     |                           | ns   |

| RD Assert Pulse Width                                         | $\overline{RD}_{LOW}$  | 1.5 JCLK <sup>2</sup> |     |                           | ns   |

| RD Deassert Pulse Width                                       | $\overline{RD}_{HIGH}$ | 1.5 JCLK <sup>2</sup> |     |                           | ns   |

| RD Deassert to Next DREQ                                      | t <sub>DREQWAIT</sub>  | 2.5 JCLK <sup>2</sup> |     | $3.5 \times JCLK + 7.5^2$ | ns   |

| RD Deassert to DACK Deassert                                  | t <sub>RD_DACK</sub>   | 0                     |     |                           | ns   |

$<sup>^{1}</sup>$  Applies to assigned DMA channel if EDMOD0 or EDMOD1 <14:11> is programmed to a nonzero value.

<sup>&</sup>lt;sup>2</sup> For a definition of JCLK, see Figure 32.

Figure 16. Burst Read Cycle for DREQ/DACK DMA Mode for Assigned DMA Channel (EMOD0/EDMOD1[14:11] Not Programmed to a Value of 0

Figure 17. Burst Read Cycle for DREQ/DACK DMA Mode for Assigned DMA Channel (EMOD0/EDMOD1[14:11] Programmed to a Value of 0000)

Figure 18. Burst Read Cycle for Fly-By DMA Mode

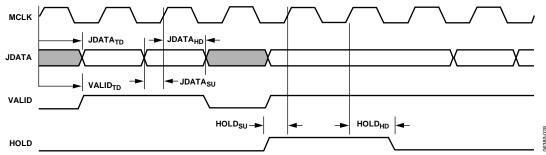

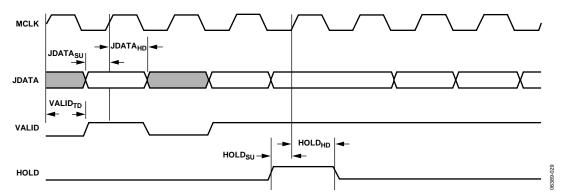

## STREAMING MODE (JDATA)—FIFO READ/WRITE

Table 10.

| Parameter                     | Mnemonic                   | Min                   | Тур | Max                         | Unit |

|-------------------------------|----------------------------|-----------------------|-----|-----------------------------|------|

| MCLK to JDATA Valid           | JDATA <sub>TD</sub>        | 1.5 JCLK <sup>1</sup> |     | $2.5 \times JCLK + 9.5^{1}$ | ns   |

| MCLK to VALID Assert/Deassert | VALID <sub>TD</sub>        | 1.5 JCLK <sup>1</sup> |     | $2.5 \times JCLK + 8.0^{1}$ | ns   |

| HOLD Setup to Rising MCLK     | HOLDsu                     | 3                     |     |                             | ns   |

| HOLD Hold from Rising MCLK    | HOLD <sub>HD</sub>         | 3                     |     |                             | ns   |

| JDATA Setup to Rising MCLK    | <b>JDATA</b> <sub>SU</sub> | 3                     |     |                             | ns   |

| JDATA Hold from Rising MCLK   | JDATA <sub>HD</sub>        | 3                     |     |                             | ns   |

<sup>&</sup>lt;sup>1</sup> For a definition of JCLK, see Figure 32.

Figure 19. Streaming Mode Timing—Encode Mode JDATA Output

Figure 20. Streaming Mode Timing—Decode Mode JDATA Input

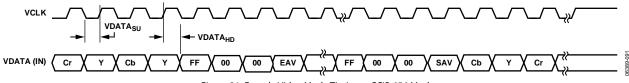

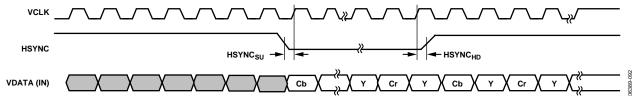

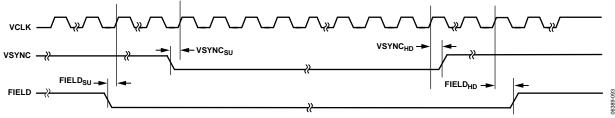

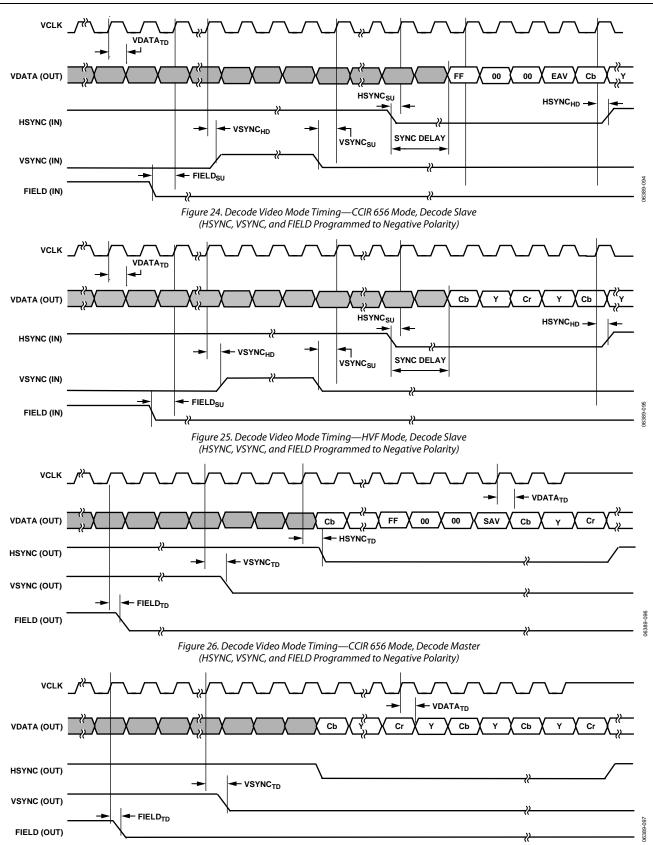

#### **VDATA MODE TIMING**

Table 11.

| Parameter                                                                 | Mnemonic                   | Min | Тур | Max | Unit        |

|---------------------------------------------------------------------------|----------------------------|-----|-----|-----|-------------|

| VCLK to VDATA Valid Delay (VDATA Output)                                  | <b>VDATA</b> <sub>TD</sub> |     |     | 12  | ns          |

| VDATA Setup to Rising VCLK (VDATA Input)                                  | <b>VDATA</b> <sub>SU</sub> | 4   |     |     | ns          |

| VDATA Hold from Rising VCLK (VDATA Input)                                 | VDATA <sub>HD</sub>        | 4   |     |     | ns          |

| HSYNC Setup to Rising VCLK                                                | HSYNC <sub>SU</sub>        | 3   |     |     | ns          |

| HSYNC Hold from Rising VCLK                                               | HSYNC <sub>HD</sub>        | 4   |     |     | ns          |

| VCLK to HSYNC Valid Delay                                                 | HSYNC <sub>TD</sub>        |     |     | 12  | ns          |

| VSYNC Setup to Rising VCLK                                                | <b>VSYNC</b> <sub>SU</sub> | 3   |     |     | ns          |

| VSYNC Hold from Rising VCLK                                               | VSYNC <sub>HD</sub>        | 4   |     |     | ns          |

| VCLK to VSYNC Valid Delay                                                 | <b>VSYNC</b> <sub>TD</sub> |     |     | 12  | ns          |

| FIELD Setup to Rising VCLK                                                | FIELDsu                    | 4   |     |     | ns          |

| FIELD Hold from Rising VCLK                                               | FIELD <sub>HD</sub>        | 3   |     |     | ns          |

| VCLK to FIELD Valid                                                       | FIELD <sub>TD</sub>        |     |     | 12  |             |

| Decode Slave Data Sync Delay<br>(HSYNC Low to First 0xFF of EAV/SAV Code) | SYNC DELAY                 |     | 81  |     | VCLK cycles |

| Decode Slave Data Sync Delay<br>(HSYNC Low to First Data for HVF Mode)    |                            |     | 10¹ |     | VCLK cycles |

<sup>&</sup>lt;sup>1</sup> The sync delay value varies according to the application.

Figure 21. Encode Video Mode Timing—CCIR 656 Mode

Figure 22. Encode Video Mode Timing—HVF Mode (HSYNC Timing) (HSYNC Programmed for Negative Polarity)

Figure 23. Encode Video Mode Timing—HVF Mode (VSYNC and FIELD Timing) (VSYNC and FIELD Programmed for Negative Polarity)

Figure 27. Decode Video Mode Timing—HVF Mode, Decode Master (HSYNC, VSYNC, and FIELD Programmed to Negative Polarity)

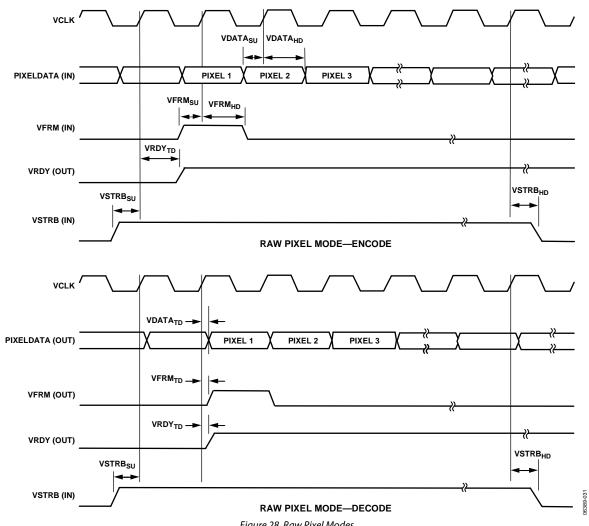

#### **RAW PIXEL MODE TIMING**

Table 12.

| Parameter                                         | Mnemonic                   | Min | Тур | Max | Unit |

|---------------------------------------------------|----------------------------|-----|-----|-----|------|

| VCLK to PIXELDATA Valid Delay (PIXELDATA Output)  | <b>VDATA</b> <sub>TD</sub> |     |     | 12  | ns   |

| PIXELDATA Setup to Rising VCLK (PIXELDATA Input)  | <b>VDATA</b> <sub>SU</sub> | 4   |     |     | ns   |

| PIXELDATA Hold from Rising VCLK (PIXELDATA Input) | <b>VDATA</b> <sub>HD</sub> | 4   |     |     | ns   |

| VCLK to VRDY Valid Delay                          | $VRDY_{TD}$                |     |     | 12  | ns   |

| VFRM Setup to Rising VCLK (VFRAME Input)          | <b>VFRM</b> <sub>SU</sub>  | 3   |     |     | ns   |

| VFRM Hold from Rising VCLK (VFRAME Input)         | VFRM <sub>HD</sub>         | 4   |     |     | ns   |

| VCLK to VFRM Valid Delay (VFRAME Output)          | <b>VFRM</b> <sub>TD</sub>  |     |     | 12  | ns   |

| VSTRB Setup to Rising VCLK                        | <b>VSTRB</b> <sub>SU</sub> | 4   |     |     | ns   |

| VSTRB Hold from Rising VCLK                       | <b>VSTRB</b> <sub>HD</sub> | 3   |     |     | ns   |

Figure 28. Raw Pixel Modes

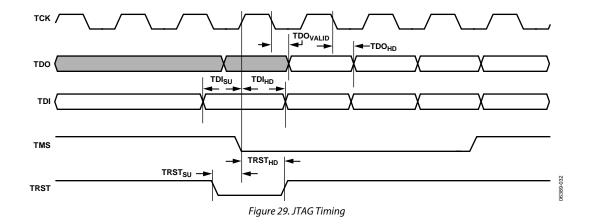

## **JTAG TIMING**

Table 13.

| Parameter             | Mnemonic             | Min | Тур | Max  | Unit       |

|-----------------------|----------------------|-----|-----|------|------------|

| TCK Period            | TCK                  | 134 |     |      | ns         |

| TDI or TMS Setup Time | TDI <sub>SU</sub>    | 4.0 |     |      | ns         |

| TDI or TMS Hold Time  | TDI <sub>HD</sub>    | 4.0 |     |      | ns         |

| TDO Hold Time         | TDO <sub>HD</sub>    | 0.0 |     |      | ns         |

| TDO Valid             | TDO <sub>VALID</sub> |     |     | 10.0 | ns         |

| TRST Hold Time        | TRST <sub>HD</sub>   | 4.0 |     |      | ns         |

| TRST Setup Time       | TRST <sub>SU</sub>   | 4.0 |     |      | ns         |

| TRST Pulse Width Low  | TRST <sub>LOW</sub>  | 4   |     |      | TCK cycles |

## **ABSOLUTE MAXIMUM RATINGS**

Table 14.

| Parameter                               | Rating                   |

|-----------------------------------------|--------------------------|

| VDD – Supply Voltage, Core              | −0.3 V to +1.65 V        |

| IOVDD – Supply Voltage,<br>Input/Output | -0.3 V to +3.63 V        |

| Storage Temperature (Ts)                | −65°C to +150°C          |

| Reflow Soldering                        |                          |

| RoHS-compliant, 121-Ball                | 260°C (20 sec to 40 sec) |

| RoHS-compliant, 144-Ball                | 260°C (20 sec to 40 sec) |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 15. Thermal Resistance

| Package Type        | θја  | <b>Ө</b> лс | Unit |

|---------------------|------|-------------|------|

| 144-Ball ADV212BBCZ | 22.5 | 3.8         | °C/W |

| 121-Ball ADV212BBCZ | 32.8 | 7.92        | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

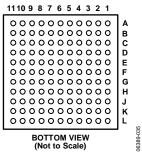

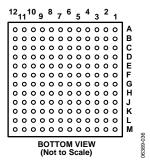

Figure 30.121-Ball Pin Configuration

Figure 31. 144-Ball Pin Configuration

**Table 16. Pin Function Descriptions**

| 121-Bal                                                       | l Package                                                        | 144-Ball                                                       | Package                                                          |                   |              |      |                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------|-------------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                                       | Location                                                         | Pin No.                                                        | Location                                                         | Mnemonic          | Pins<br>Used | Туре | Description                                                                                                                                                                                                                                                                                                                            |

| 119                                                           | L9                                                               | 132                                                            | L12                                                              | MCLK              | 1            | I    | System Input Clock. See the PLL section.                                                                                                                                                                                                                                                                                               |

| 117                                                           | L7                                                               | 131                                                            | L11                                                              | RESET             | 1            | 1    | Reset. Causes the ADV212 to immediately reset. CS, RD, WE, DACK0, DACK1, DREQ0, and DREQ1 must be held high when a RESET is applied.                                                                                                                                                                                                   |

| 37 to 34,<br>27 to 25,<br>16, 15, 24,<br>14 to 12,<br>2, 6, 5 | D4 to D1,<br>C5 to C3,<br>B5, B4, C2,<br>B3 to B1,<br>A2, A6, A5 | 64, 49 to<br>51, 37 to<br>39, 25 to<br>27, 13 to<br>15, 2 to 4 | F4, E1 to E3,<br>D1 to D3,<br>C1 to C3,<br>B1 to B3,<br>A2 to A4 | HDATA[15:0]       | 16           | I/O  | Host Data Bus. With HDATA[23:16], HDATA[27:24], and HDATA[31:28], these pins make up the 32-bit wide host data bus. The async host interface is interfaced together with ADDR[3:0], $\overline{CS}$ , $\overline{WE}$ , $\overline{RD}$ , and $\overline{ACK}$ . Unused HDATA pins should be pulled down via a 10 k $\Omega$ resistor. |

| 88, 107,<br>87, 97                                            | H11, K8,<br>H10, J9                                              | 108 to 106,<br>96                                              | J12 to J10,<br>H12                                               | ADDR[3:0]         | 4            | 1    | Address Bus for the Host Interface.                                                                                                                                                                                                                                                                                                    |

| 96                                                            | J8                                                               | 95                                                             | H11                                                              | <u>cs</u>         | 1            | 1    | Chip Select. This signal is used to qualify addressed read and write access to the ADV212 using the host interface.                                                                                                                                                                                                                    |

| 95                                                            | J7                                                               | 94                                                             | H10                                                              | WE¹               | 1            | 1    | Write Enable Used with the Host Interface.                                                                                                                                                                                                                                                                                             |

|                                                               |                                                                  |                                                                |                                                                  | RDFB <sup>2</sup> |              |      | Read Enable When Fly-By DMA Is Enabled. Simultaneous assertion of WE and DACK low activates the HDATA bus, even if the DMA channels are disabled.                                                                                                                                                                                      |

| 86                                                            | H9                                                               | 84                                                             | G12                                                              | RD <sup>1</sup>   | 1            | 1    | Read Enable Used with the Host Interface.                                                                                                                                                                                                                                                                                              |

|                                                               |                                                                  |                                                                |                                                                  | WEFB <sup>3</sup> |              |      | Write Enable When Fly-By <u>DM</u> A Is <u>Enabled</u> . Simultaneous assertion of RD and DACK low activates the HDATA bus, even if the DMA channels are disabled.                                                                                                                                                                     |

| 121-Ba  | l Package | 144-Ba  | all Package |          |              |      |                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------|---------|-------------|----------|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Location  | Pin No. | Location    | Mnemonic | Pins<br>Used | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                |

| 85      | H8        | 83      | G11         | ACK      | 1            | 0    | Acknowledge. Used for direct register accesses. This signal indicates that the last register access was successful. Due to synchronization issues, control and status register accesses may incur an additional delay; therefore, the host software should wait for acknowledgment from the ADV212 before attempting another register access.  Accesses to the FIFOs (external DMA modes), |

|         |           |         |             |          |              |      | on the other hand, are guaranteed to occur immediately, provided that space is available; therefore, the host software does not need to wait for ACK before attempting another register access, provided that the timing constraints                                                                                                                                                       |

|         |           |         |             |          |              |      | are observed. If $\overline{ACK}$ is shared with more than one device, $\overline{ACK}$ should be connected to a pull-up resistor (10 k $\Omega$ ) and the PLL_HI register, Bit 4, must be set to 1.                                                                                                                                                                                       |

| 76      | G10       | 82      | G10         | ĪRQ      | 1            | 0    | Interrupt. This pin indicates that the ADV212 requires the attention of the host processor. This pin can be programmed to indicate the status of the internal interrupt conditions within the ADV212. The interrupt sources are enabled via the bits in the EIRQIE register.                                                                                                               |

| 63      | F8        | 72      | F12         | DREQ0    | 1            | 0    | Data Request for External DMA Interface.<br>Indicates that the ADV212 is ready to<br>send/receive data to/from the FIFO assigned<br>to DMA Channel 0.                                                                                                                                                                                                                                      |

|         |           |         |             | FSRQ0    |              | 0    | FIFO Service Request. Used in DCS-DMA<br>Mode. Service request from the FIFO assigned<br>to Channel 0 (asynchronous mode).                                                                                                                                                                                                                                                                 |

|         |           |         |             | VALID    |              | 0    | Valid Indication for JDATA Input/Output Stream. Polarity of this pin is programmable in the EDMOD0 register. VALID is always an output.                                                                                                                                                                                                                                                    |

|         |           |         |             | CFG1     |              | 1    | Boot Mode Configuration. This pin is read on reset to determine the boot configuration of the on-board processor. The pin should be tied to IOVDD or DGND through a 10 k $\Omega$ resistor.                                                                                                                                                                                                |

| 64      | F9        | 71      | F11         | DACKO    | 1            | I    | Data Acknowledge for External DMA Interface. Signal from the host CPU, which indicates that the data transfer request (DREQ0) has been acknowledged and that the data transfer can proceed. This pin must be held high at all times if the DMA interface is not used, even if the DMA channels are disabled.                                                                               |

|         |           |         |             | HOLD     |              | I    | External Hold Indication for JDATA Input/Output Stream. Polarity is programmable in the EDMOD0 register. This pin is always an input.                                                                                                                                                                                                                                                      |

|         |           |         |             | FCS0     |              | I    | FIFO Chip Select. Used in DCS-DMA mode.<br>Chip select for the FIFO assigned to Channel 0<br>(asynchronous mode).                                                                                                                                                                                                                                                                          |

| 121-Ball          | Package           | 144-Ball         | Package      |              |              |      |                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-------------------|------------------|--------------|--------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.           | Location          | Pin No.          | Location     | Mnemonic     | Pins<br>Used | Туре | Description                                                                                                                                                                                                                                                                                                                                                                            |

| 65                | F10               | 70               | F10          | DREQ1        | 1            | 0    | Data Request for External DMA Interface. Indicates that the ADV212 is ready to send/receive data to/from the FIFO assigned to DMA Channel 1.                                                                                                                                                                                                                                           |

|                   |                   |                  |              | FSRQ1        |              | 0    | FIFO Service Request. Used in DCS-DMA<br>Mode. Service request from the FIFO assigned<br>to Channel 1 (asynchronous mode).                                                                                                                                                                                                                                                             |

|                   |                   |                  |              | CFG2         |              | I    | Boot Mode Configuration. This pin is read on reset to determine the boot configuration of the on-board processor. The pin should be tied to IOVDD or DGND through a 10 k $\Omega$ resistor.                                                                                                                                                                                            |

| 75                | G9                | 69               | F9           | DACK1        | 1            | 1    | Data Acknowledge for External DMA Interface. Signal from the host CPU, which indicates that the data transfer request (DREQ1) has been acknowledged and data transfer can proceed. This pin must be held high at all times unless a DMA or JDATA access is occurring. This pin must be held high at all times if the DMA interface is not used, even if the DMA channels are disabled. |

|                   |                   |                  |              | FCS1         |              | I    | FIFO Chip Select. Used in DCS-DMA mode.<br>Chip select for the FIFO assigned to Channel 1<br>(asynchronous mode).                                                                                                                                                                                                                                                                      |

| 90 to 92, 78      | J2 to J4, H1      | 111, 97 to<br>99 | K3, J1 to J3 | HDATA[31:28] | 4            | I/O  | Host Expansion Bus.                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                   |                  |              | JDATA[7:4]   |              | I/O  | JDATA Bus (JDATA Mode).                                                                                                                                                                                                                                                                                                                                                                |

| 79 to 81, 70      | H2 to H4, G4      | 100, 85 to<br>87 | J4, H1 to H3 | HDATA[27:24] | 4            | I/O  | Host Expansion Bus.                                                                                                                                                                                                                                                                                                                                                                    |

| 60.60             | 62.62             | 00 72 +- 75      | 114 C1 to C2 | JDATA[3:0]   | 4            | 1/0  | JDATA Bus (JDATA Mode).                                                                                                                                                                                                                                                                                                                                                                |

| 69, 68,<br>59, 58 | G3, G2,<br>F4, F3 | 88, 73 to 75     | H4, G1 to G3 | HDATA[23:20] | 4            | I/O  | Host Expansion Bus.                                                                                                                                                                                                                                                                                                                                                                    |

| 57, 46 to 48      | F2, E2, E3,<br>E4 | 76, 61 to 63     | G4, F1 to F3 | HDATA[19:16] | 4            | I/O  | Host Expansion Bus.                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                   |                  |              | VDATA[15:12] |              | I/O  | Video Data. Used only for raw pixel video mode. Unused pins should be pulled down via a 10 kΩ resistor.                                                                                                                                                                                                                                                                                |

| 112               | L2                | 134              | M2           | SCOMM7       | 8            | I/O  | Serial Communication. For internal use only. This pin should be tied low via a 10 $k\Omega$ resistor.                                                                                                                                                                                                                                                                                  |

| 113               | L3                | 135              | M3           | SCOMM6       |              | I/O  | Serial Communication. For internal use only. This pin should be tied low via a 10 $k\Omega$ resistor.                                                                                                                                                                                                                                                                                  |

| 114               | L4                | 136              | M4           | SCOMM5       |              | I/O  | Serial Communication. This pin must be used in multiple chip mode to align the outputs of two or more ADV212s. For details, see the Applications section and Application Note AN-796 . When not used, this pin should be tied low via a 10 k $\Omega$ resistor.                                                                                                                        |

| 100               | K1                | 121              | L1           | SCOMM4       |              | 0    | LCODE Output in Encode Mode. When LCODE is enabled, the output on this pin indicates on a high transition that the last data-word for a field has been read from the FIFO. For an 8-bit interface, such as JDATA, LCODE is asserted for four consecutive bytes and is enabled by default.                                                                                              |

| 121-Ball                                             | Package                                                          | 144-Ball                                                                 | Package                                                         |               |              |      |                                                                                                                                                                                             |

|------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|---------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                              | Location                                                         | Pin No.                                                                  | Location                                                        | Mnemonic      | Pins<br>Used | Туре | Description                                                                                                                                                                                 |

| 101                                                  | K2                                                               | 122                                                                      | L2                                                              | SCOMM3        |              | I    | Serial Communication. For internal use only. This pin should be tied low via a $10 \text{ k}\Omega$ resistor.                                                                               |

| 115                                                  | L5                                                               | 123                                                                      | L3                                                              | SCOMM2        |              | 0    | Serial Communication. For internal use only. This pin should be tied low via a 10 k $\Omega$ resistor.                                                                                      |

| 103                                                  | K4                                                               | 109                                                                      | K1                                                              | SCOMM1        |              | I    | Serial Communication. For internal use only. This pin should be tied low via a 10 k $\Omega$ resistor.                                                                                      |

| 102                                                  | K3                                                               | 110                                                                      | K2                                                              | SCOMM0        |              | 0    | Serial Communication. This pin should be tied low via a 10 k $\Omega$ resistor.                                                                                                             |

| 53                                                   | E9                                                               | 60                                                                       | E12                                                             | VCLK          | 1            | 1    | Video Data Clock. This pin must be supplied if video data is input/output on the VDATA bus.                                                                                                 |

| 44, 43, 29,<br>31, 32, 18<br>to 20, 22,<br>21, 7, 10 | D11, D10,<br>C7, C9, C10,<br>B7, B8, B9,<br>B11, B10,<br>A7, A10 | 46 to 48,<br>34 to 36,<br>22 to 24,<br>9 to 11                           | D10 to D12,<br>C10 to C12,<br>B10 to B12,<br>A9 to A11          | VDATA[11:0]   | 12           | I/O  | Video Data. Unused pins should be pulled down via a 10 k $\Omega$ resistor.                                                                                                                 |

| 41                                                   | D8                                                               | 58                                                                       | E10                                                             | VSYNC<br>VFRM | 1            | I/O  | Vertical Sync for Video Mode. Raw Pixel Mode Framing Signal. When this pin is asserted high, it indicates the first sample of a tile.                                                       |

| 42                                                   | D9                                                               | 59                                                                       | E11                                                             | HSYNC         | 1            | I/O  | Horizontal Sync for Video Mode.                                                                                                                                                             |

|                                                      |                                                                  |                                                                          |                                                                 | VRDY          |              | 0    | Raw Pixel Mode Ready Signal.                                                                                                                                                                |

| 54                                                   | E10                                                              | 57                                                                       | E9                                                              | FIELD         | 1            | I/O  | Field Sync for Video Mode.                                                                                                                                                                  |

| 0.4                                                  | 16                                                               | 120                                                                      | K12                                                             | VSTRB         |              |      | Raw Pixel Mode Transfer Strobe.                                                                                                                                                             |

| 94                                                   | J6                                                               | 120                                                                      | K12                                                             | TCK           | 1            | I    | JTAG Clock. If not used, this pin should be connected to ground via a pull-down resistor.                                                                                                   |

| 108                                                  | K9                                                               | 119                                                                      | K11                                                             | TRS           | 1            |      | JTAG Reset. If the JTAG is used, this pin must<br>be toggled low to high. If JTAG is not used,<br>this pin must be held low.                                                                |

| 98                                                   | J10                                                              | 118                                                                      | K10                                                             | TMS           | 1            | I    | JTAG Mode Select. If JTAG is used, connect a 10 k $\Omega$ pull-up resistor to this pin. If not used, this pin should be connected to ground via a pull-down resistor.                      |

| 116                                                  | L6                                                               | 141                                                                      | M9                                                              | TDI           | 1            | I    | JTAG Serial Data Input. If JTAG is used, connect a $10 \text{ k}\Omega$ pull-up resistor to this pin. If JTAG is not used, this pin should be connected to ground via a pull-down resistor. |

| 109                                                  | K10                                                              | 130                                                                      | L10                                                             | TDO           | 1            | 0    | JTAG Serial Data Output. If this pin is not used, do not connect it.                                                                                                                        |

| 3, 8, 40, 84,<br>120                                 | A3, A8, D7,<br>H7, L10                                           | 18, 19, 30,<br>31, 42, 43,<br>102, 103,<br>114, 115,<br>126, 127,<br>142 | B6, B7, C6,<br>C7, D6, D7,<br>J6, J7, K6,<br>K7, L6, L7,<br>M10 | VDD           | 5/13         | V    | Positive Supply for Core.                                                                                                                                                                   |

| 121-Ball                                                                                                                                | Package                                                                                                                                            | 144-Ball                                                                                                                                                                 | Package                                                                                                                                                                |          |              |      |                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|------|-----------------------------------|

| Pin No.                                                                                                                                 | Location                                                                                                                                           | Pin No.                                                                                                                                                                  | Location                                                                                                                                                               | Mnemonic | Pins<br>Used | Туре | Description                       |

| 1, 4, 9,11,<br>23, 33, 39,<br>45, 49 to<br>51, 55, 56,<br>60 to 62,<br>66, 67, 71<br>to 73, 77,<br>83, 89, 99,<br>110, 111,<br>118, 121 | A1, A4, A9,<br>A11, C1,<br>C11, D6, E1,<br>E5 to E7,<br>E11, F1, F5<br>to F7, F11,<br>G1, G5 to<br>G7, G11,<br>H6, J1, J11,<br>K11, L1, L8,<br>L11 | 1, 5 to 8, 12,<br>17, 20, 29,<br>32, 41, 44,<br>52 to 56, 65<br>to 68, 77 to<br>81, 89 to<br>93, 101,<br>104, 105,<br>113, 116,<br>125, 128,<br>133, 137 to<br>140, 143, | A1, A5 to<br>A8, A12, B5,<br>B8, C5, C8,<br>D5, D8, E4<br>to E8, F5 to<br>F8, G5 to<br>G9, H5 to<br>H9, J5, J8,<br>J9, K5, K8,<br>L5, L8, M1,<br>M5 to M8,<br>M11, M12 | DGND     | 29/45        | GND  | Ground.                           |

| 17, 28, 30,<br>38, 52, 74,<br>82, 93, 104<br>to 106                                                                                     | B6, C6, C8,<br>D5, E8, G8,<br>H5, J5, K5<br>to K7                                                                                                  | 144<br>16, 21, 28,<br>33, 40, 45,<br>112, 117,<br>124, 129                                                                                                               | B4, B9, C4,<br>C9, D4, D9,<br>K4, K9, L4,<br>L9                                                                                                                        | IOVDD    | 11/10        | V    | Positive Supply for Input/Output. |

<sup>&</sup>lt;sup>1</sup> In fly-by mode DMA, the function of the  $\overline{RD}$  and  $\overline{WE}$  signals (for DMA only) are reversed. This allows a host to move data between an external device and the ADV212 with the use of a single strobe.

In encode mode with fly-by DMA, the host can use the RDFB signal (WE pin) to simultaneously read from the ADV212 and write to an external device such as memory.

In decode mode with fly-by DMA, the host can use the WEFB signal (RD pin) to simultaneously read from the external device and write to the ADV212.

## THEORY OF OPERATION

The input video or pixel data is passed to the ADV212 pixel interface, and samples are deinterleaved and passed to the wavelet engine, which decomposes each tile or frame into subbands using the 5/3 or 9/7 filters. The resultant wavelet coefficients are then written to the internal memory. The entropy codecs code the image data so that it conforms to the JPEG2000 standard. An internal DMA provides high bandwidth memory-to-memory transfers, as well as high performance transfers between functional blocks and memory.

#### **WAVELET ENGINE**

The ADV212 provides a dedicated wavelet transform processor based on the Analog Devices proven and patented SURF\* technology. This processor can perform up to six wavelet decomposition levels on a tile. In encode mode, the wavelet transform processor takes in uncompressed samples, performs the wavelet transform and quantization, and writes the wavelet coefficients in all frequency subbands to the internal memory. Each of these subbands is further broken down into code blocks. The code-block dimensions can be user defined and are used by the wavelet transform processor to organize the wavelet coefficients into code blocks when writing to the internal memory. Each completed code block is then entropy coded by one of the entropy codecs.

In decode mode, wavelet coefficients are read from internal memory and recomposed into uncompressed samples.

#### **ENTROPY CODECS**

The entropy codec block performs context modeling and arithmetic coding on a code block of the wavelet coefficients. Additionally, this block also performs the distortion metric calculations during compression that are required for optimal rate and distortion performance. Because the entropy coding process is the most computationally intensive operation in the JPEG2000 compression process, three dedicated hardware entropy codecs are provided on the ADV212.

#### **EMBEDDED PROCESSOR SYSTEM**

The ADV212 incorporates an embedded 32-bit RISC processor. This processor is used for configuration, control, and management of the dedicated hardware functions, as well as for parsing and generating the JPEG2000 code stream. The processor system includes memory for both the program and data memory, the interrupt controller, the standard bus interfaces, and other hardware functions such as timers and counters.

#### **MEMORY SYSTEM**

The main function of the memory system is to manage wavelet coefficient data, interim code-block attribute data, and temporary workspace for creating, parsing, and storing the JPEG2000 code stream. The memory system can also be used for the program and data memory for the embedded processor.

#### **INTERNAL DMA ENGINE**

The internal DMA engine provides high bandwidth memory-to-memory transfers, as well as high performance transfers between memory and functional blocks. This function is critical for high speed generation and parsing of the code stream.

## **ADV212 INTERFACES**

There are several possible ways to interface to the ADV212 using the VDATA bus and the HDATA bus or the HDATA bus alone.

#### **VIDEO INTERFACE (VDATA BUS)**

The video interface can be used in applications in which uncompressed pixel data is on a separate bus from compressed data. For example, it is possible to use the VDATA bus to input uncompressed video while using the HDATA bus to output the compressed data. This interface is ideal for applications requiring very high throughput, such as live video capture.

Optionally, the ADV212 interlaces ITU-R BT.656 resolution video on the fly prior to wavelet processing, which yields significantly better compression performance for temporally coherent frame-based video sources. Additionally, high definition digital video such as SMPTE 274M (1080i) is supported using two or more ADV212 devices.

The video interface can support video data or still image data input/output in 8-/10-/12-bit formats, in YCbCr format, or in single input mode. YCbCr data must be in 4:2:2 format.

Video data can be input/output in several different modes on the VDATA bus, as described in Table 17. In all these modes, the pixel clock must be input on the VCLK pin.

Table 17. Video Input/Output Modes

| Mode         | Description                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| EAV/SAV      | Accepts video with embedded EAV/SAV codes, where the YCbCr data is interleaved onto a single bus.                               |

| HVF          | Accepts video data accompanied by separate H, V, and F signals, where YCbCr data is interleaved onto a single bus.              |

| Raw<br>Video | Used for still picture data and nonstandard video.<br>VFRM, VSTRB, and VRDY are used to program the<br>dimensions of the image. |

#### **HOST INTERFACE (HDATA BUS)**