## **KSZ9021GQ**

# Gigabit Ethernet Transceiver with GMII / MII Support

Data Sheet Rev. 1.0

# **General Description**

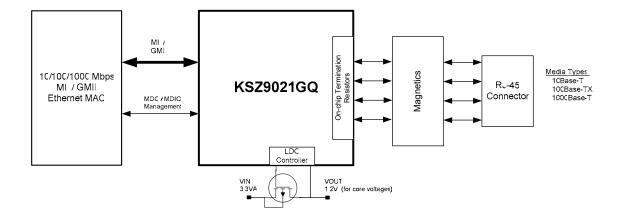

The KSZ9021GQ is a completely integrated triple speed (10Base-T/100Base-TX/1000Base-T) Ethernet Physical Layer Transceiver for transmission and reception of data on standard CAT-5 unshielded twisted pair (UTP) cable.

The KSZ9021GQ provides the industry standard GMII/MII (Gigabit Media Independent Interface / Media Independent Interface) for direct connection to GMII/MII MACs in Gigabit Ethernet Processors and Switches for data transfer at 1000 Mbps or 10/100 Mbps speed.

The KSZ9021GQ reduces board cost and simplifies board layout by using on-chip termination resistors for the four differential pairs and by integrating a LDO controller to drive a low cost MOSFET to supply the 1.2V core.

The KSZ9021GQ provides diagnostic features to facilitate system bring-up and debugging in production testing and in product deployment. Parametric NAND tree support enables fault detection between KSZ9021 I/Os and board. Micrel LinkMD® TDR-based cable diagnostics permit identification of faulty copper cabling. Remote and local loopback functions provide verification of analog and digital data paths.

The KSZ9021GQ is available in a 128-pin, lead-free PQFP package (See Ordering Information).

### **Features**

- Single-chip 10/100/1000 Mbps IEEE 802.3 compliant Ethernet Transceiver

- GMII/MII standard compliant interface

- Auto-negotiation to automatically select the highest link up speed (10/100/100 Mbps) and duplex (half/full)

- On-chip termination resistors for the differential pairs

- On-chip LDO controller to support single 3.3V supply operation – requires only external FET to generate 1.2V for the core

- Jumbo frame support up to 16KB

- 125MHz Reference Clock Output

- Programmable LED outputs for link, activity and speed

- Baseline Wander Correction

- LinkMD<sup>®</sup> TDR-based cable diagnostics for identification of faulty copper cabling

- Parametric NAND Tree support for fault detection between chip I/Os and board.

- Loopback modes for diagnostics

- Automatic MDI/MDI-X crossover for detection and correction of pair swap at all speeds of operation

# **Functional Diagram**

LinkMD is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

January 2009 M9999-011609-1.0

### **More Features**

- Automatic detection and correction of pair swaps, pair skew and pair polarity

- MDC/MDIO Management Interface for PHY register configuration

- Interrupt pin option

- Power down and power saving modes

- Operating Voltages

Core: 1.2V (external FET or regulator)

I/O: 3.3V Transceiver: 3.3V

• Available in 128-pin PQFP (14mm x 20mm) package

# **Applications**

- Laser/Network Printer

- Network Attached Storage (NAS)

- Network Server

- Gigabit LAN on Motherboard (GLOM)

- · Broadband Gateway

- Gigabit SOHO/SMB Router

- IPTV

- IP Set-top Box

- Game Console

- Triple-play (data, voice, video) Media Center

- Media Converter

# **Ordering Information**

| Part Number    | Temp. Range   | Гетр. Range Package Lead Finish De |         | Description                        |

|----------------|---------------|------------------------------------|---------|------------------------------------|

| KSZ9021GQ      | 0°C to 70°C   | 128-Pin PQFP                       | Pb-Free | GMII / MII, Commercial Temperature |

| KSZ9021GQI (1) | -40°C to 85°C | 128-Pin PQFP                       | Pb-Free | GMII / MII, Industrial Temperature |

#### Note:

1. Contact factory for lead time.

# **Revision History**

| Revision | Date    | Summary of Changes |  |  |  |

|----------|---------|--------------------|--|--|--|

| 1.0      | 1/16/09 | Data sheet created |  |  |  |

# **Contents**

| Pin Configuration                                           | 8  |

|-------------------------------------------------------------|----|

| Pin Description                                             | 9  |

| Strapping Options                                           | 18 |

| Functional Overview                                         | 19 |

| Functional Description: 10Base-T/100Base-TX Transceiver     | 20 |

| 100Base-TX Transmit                                         | 20 |

| 100Base-TX Receive                                          | 20 |

| Scrambler/De-scrambler (100Base-TX only)                    | 20 |

| 10Base-T Transmit                                           | 20 |

| 10Base-T Receive                                            | 20 |

| Functional Description: 1000Base-T Transceiver              | 21 |

| Analog Echo Cancellation Circuit                            | 21 |

| Automatic Gain Control (AGC)                                | 21 |

| Analog-to-Digital Converter (ADC)                           | 21 |

| Timing Recovery Circuit                                     | 22 |

| Adaptive Equalizer                                          | 22 |

| Trellis Encoder and Decoder                                 | 22 |

| Functional Description: Additional 10/100/1000 PHY Features | 22 |

| Auto MDI/MDI-X                                              | 22 |

| Pair- Swap, Alignment, and Polarity Check                   | 23 |

| Wave Shaping, Slew Rate Control and Partial Response        | 23 |

| PLL Clock Synthesizer                                       | 23 |

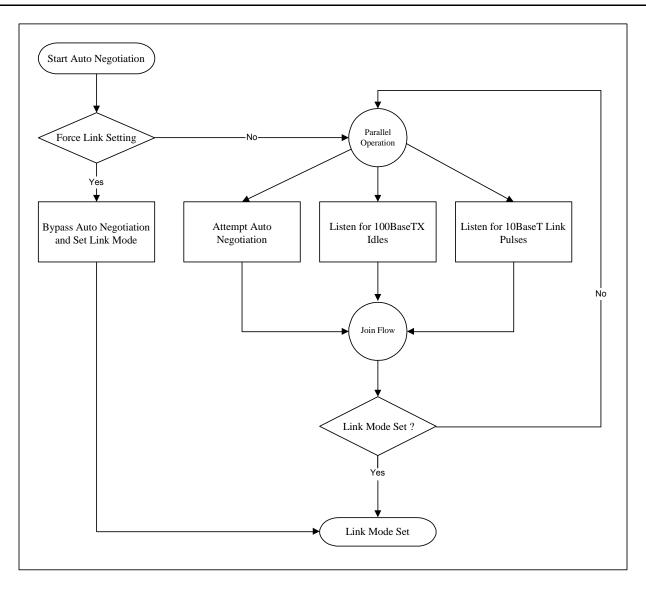

| Auto-Negotiation                                            | 23 |

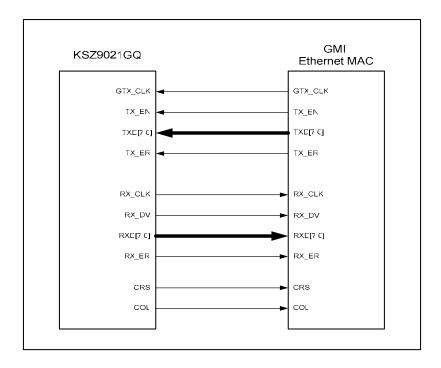

| GMII Interface                                              | 25 |

| GMII Signal Definition                                      | 26 |

| GMII Signal Diagram                                         | 26 |

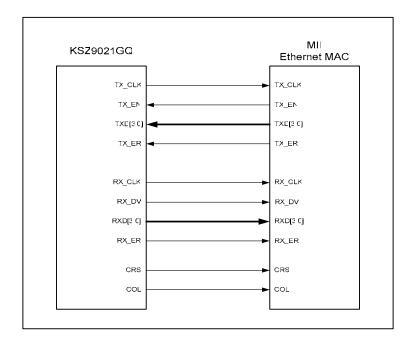

| MII Interface                                               | 27 |

| MII Signal Definition                                       | 28 |

| MII Signal Diagram                                          | 28 |

| MII Management (MIIM) Interface                             | 29 |

| Interrupt (INT_N)                                           | 29 |

| LED Mode                                                    | 29 |

| 4-LED Configuration                                         | 30 |

| 5-LED Configuration                                         | 30 |

| 6-LED Configuration                                         | 31 |

| NAND Tree Support                                           | 32 |

| Power Management                                            | 33 |

| Power Saving Mode                                           | 33 |

| Software Power Down Mode                                    | 33 |

| Chip Power Down Mode                                        | 33 |

| Register Map                                                | 34 |

| Register Description                                        | 35 |

| IEEE Defined Registers                                      | 35 |

| Vendor Specific Registers                                   | 41 |

| Extended Registers                                          |    |

| Absolute Maximum Ratings <sup>(1)</sup>                     | 45 |

| Operating Ratings <sup>(2)</sup>                            |    |

| Electrical Characteristics <sup>(3)</sup>                   | 45 |

| Timing Diagrams                          | 48 |

|------------------------------------------|----|

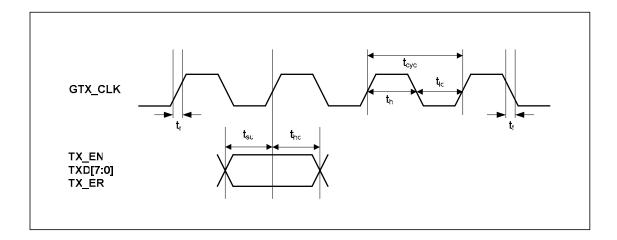

| GMII Transmit Timing                     |    |

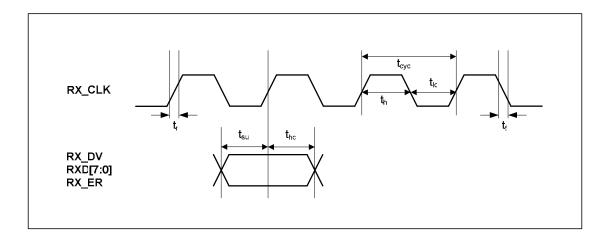

| GMII Receive Timing                      | 49 |

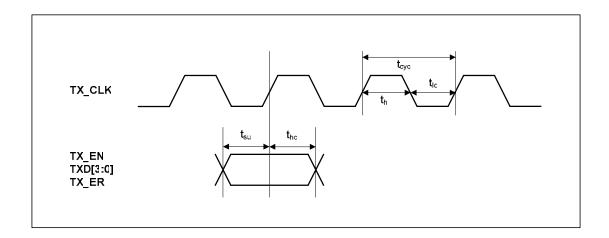

| MII Transmit Timing                      | 50 |

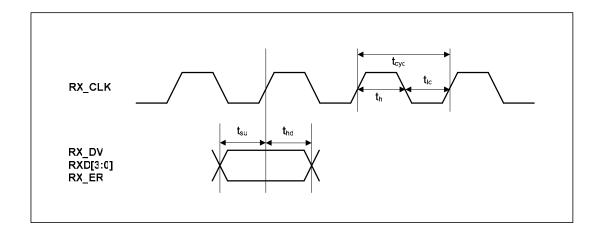

| MII Receive Timing                       | 51 |

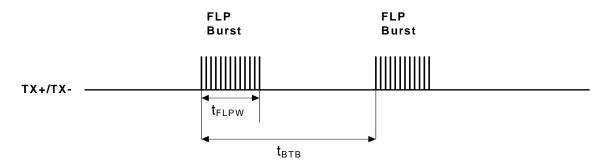

| Auto-Negotiation Timing                  | 52 |

| MDC/MDIO Timing                          | 53 |

| Reset Timing                             | 52 |

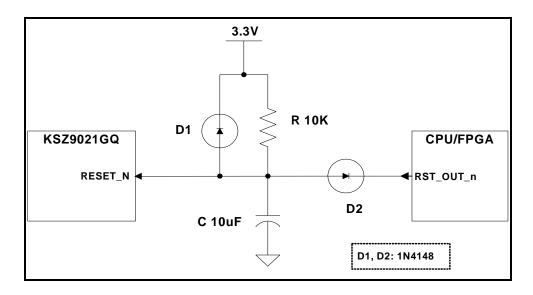

| Reset Circuit                            | 54 |

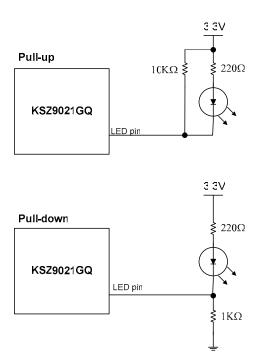

| Reference Circuits – LED Strap-in Pins   | 55 |

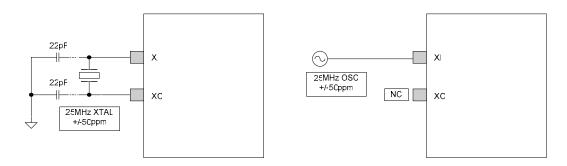

| Reference Clock – Connection & Selection | 56 |

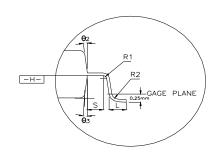

| Magnetics Specification                  | 56 |

| Package Information                      | 57 |

# **List of Figures**

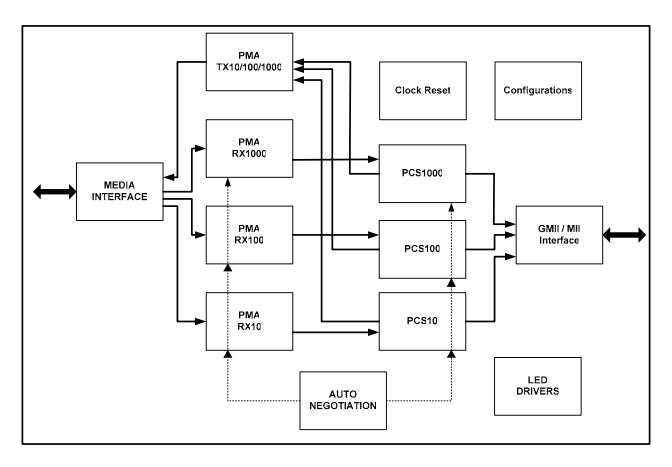

| Figure 1.  | KSZ9021GQ Block Diagram                                               | . 19 |

|------------|-----------------------------------------------------------------------|------|

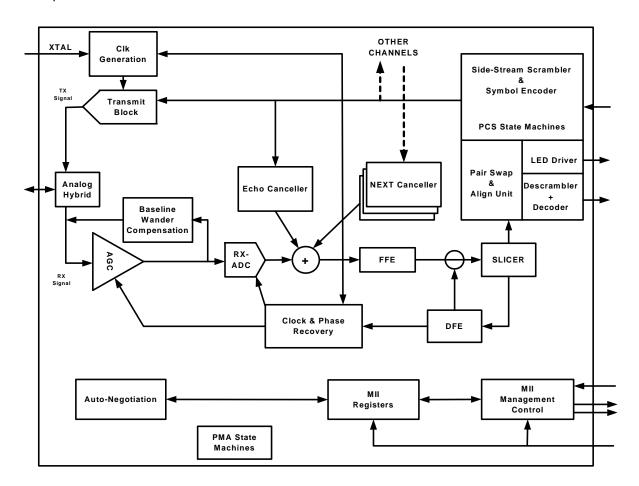

|            | KSZ9021GQ 1000Base-T Block Diagram - Single Channel                   |      |

| Figure 3.  | Auto-Negotiation Flow Chart                                           | . 24 |

| Figure 4.  | KSZ9021GQ GMII Interface                                              | . 26 |

| Figure 5.  | KSZ9021GQ MII Interface                                               | . 28 |

| Figure 6.  | GMII Transmit Timing – data input to PHY                              | . 48 |

| Figure 7.  | GMII Receive Timing – data input to MAC                               | . 49 |

| Figure 8.  | MII Transmit Timing – data input to PHY                               | . 50 |

| Figure 9.  | MII Receive Timing – data input to MAC                                | . 51 |

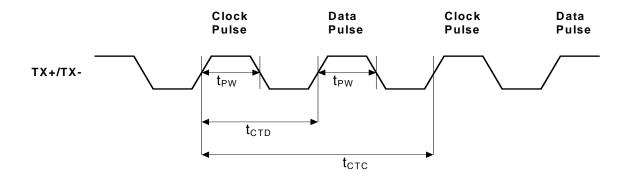

| Figure 10. | Auto-Negotiation Fast Link Pulse (FLP) Timing                         | . 52 |

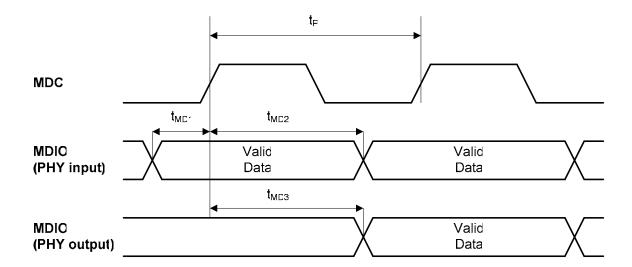

| Figure 11. | MDC/MDIO Timing                                                       | . 53 |

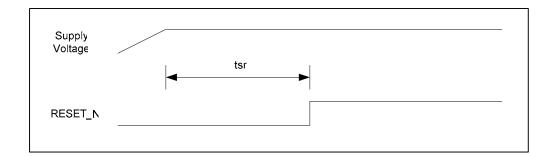

| Figure 12. | Reset Timing                                                          | . 54 |

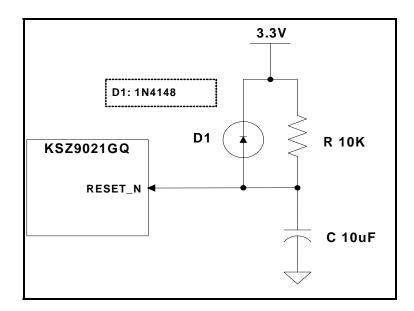

| Figure 13. | Recommended Reset Circuit                                             | . 54 |

| Figure 14. | Recommended Reset Circuit for Interfacing with CPU/FPGA Reset Output. | . 55 |

| Figure 15. | Reference Circuits for LED Strapping Pins                             | . 55 |

| Figure 16. | 25MHz Crystal / Oscillator Reference Clock Connection                 | . 56 |

# **List of Tables**

| Table 1. MDI / MDI-X Pin Mapping                                   | 22 |

|--------------------------------------------------------------------|----|

| Table 2. Auto-Negotiation Timers                                   |    |

| Table 3. GMII Signal Definition                                    |    |

| Table 4. MII Signal Definition                                     |    |

| Table 5. MII Management Frame Format – for KSZ9021GQ               | 29 |

| Table 6. 4-LED Configuration – Pin Definition                      | 30 |

| Table 7. 5-LED Configuration – Pin Definition                      |    |

| Table 8. 6-LED Configuration – Pin Definition                      |    |

| Table 9. NAND Tree Test Pin Order – for KSZ9021GQ                  | 32 |

| Table 10. GMII Transmit Timing Parameters                          | 48 |

| Table 11. GMII Receive Timing Parameters                           | 49 |

| Table 12. MII Transmit Timing Parameters                           | 50 |

| Table 13. MII Receive Timing Parameters                            | 51 |

| Table 14. Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters | 52 |

| Table 15. MDC/MDIO Timing Parameters                               | 53 |

| Table 16. Reset Timing Parameters                                  |    |

| Table 17. Reference Crystal/Clock Selection Criteria               |    |

| Table 18. Magnetics Selection Criteria                             | 56 |

| Table 19. Qualified Single Port 10/100/1000 Magnetics              | 56 |

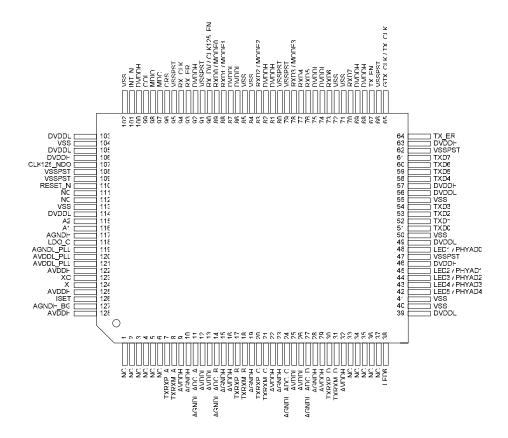

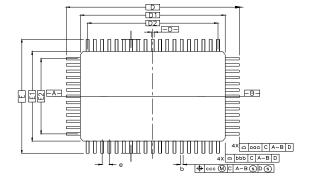

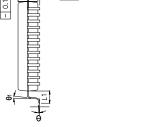

# **Pin Configuration**

128-Pin PQFP (Top View)

# **Pin Description**

| Pin Number | Pin Name    | Type <sup>(1)</sup> | Pin Function                                                                                                                                     |

|------------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NC          | -                   | No connect                                                                                                                                       |

| 2          | NC          | -                   | No connect                                                                                                                                       |

| 3          | NC          | -                   | No connect                                                                                                                                       |

| 4          | NC          | -                   | No connect                                                                                                                                       |

| 5          | NC          | -                   | No connect                                                                                                                                       |

| 6          | NC          | -                   | No connect                                                                                                                                       |

| 7          | TXRXP_A     | I/O                 | Media Dependent Interface[0], positive signal of differential pair                                                                               |

|            |             |                     | 1000Base-T Mode:                                                                                                                                 |

|            |             |                     | TXRXP_A corresponds to BI_DA+ for MDI configuration and BI_DB+ for MDI-X configuration, respectively.                                            |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                                                                      |

|            |             |                     | TXRXP_A is the positive transmit signal (TX+) for MDI configuration and the positive receive signal (RX+) for MDI-X configuration, respectively. |

| 8          | TXRXM_A     | I/O                 | Media Dependent Interface[0], negative signal of differential pair                                                                               |

|            |             |                     | 1000Base-T Mode:                                                                                                                                 |

|            |             |                     | TXRXM_A corresponds to BI_DA- for MDI configuration and BI_DB- for MDI-X configuration, respectively.                                            |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                                                                      |

|            |             |                     | TXRXM_A is the negative transmit signal (TX-) for MDI configuration and the negative receive signal (RX-) for MDI-X configuration, respectively. |

| 9          | AVDDH       | Р                   | 3.3V analog V <sub>DD</sub>                                                                                                                      |

| 10         | AGNDH       | Gnd                 | Analog ground                                                                                                                                    |

| 11         | AGNDL_ADC_A | Gnd                 | Analog ground                                                                                                                                    |

| 12         | AVDDL       | Р                   | 1.2V analog V <sub>DD</sub>                                                                                                                      |

| 13         | AVDDL       | Р                   | 1.2V analog V <sub>DD</sub>                                                                                                                      |

| 14         | AGNDL_ADC_B | Gnd                 | Analog ground                                                                                                                                    |

| 15         | AGNDH       | Gnd                 | Analog ground                                                                                                                                    |

| 16         | AVDDH       | Р                   | 3.3V analog V <sub>DD</sub>                                                                                                                      |

| 17         | TXRXP_B     | I/O                 | Media Dependent Interface[1], positive signal of differential pair                                                                               |

|            |             |                     | 1000Base-T Mode:                                                                                                                                 |

|            |             |                     | TXRXP_B corresponds to BI_DB+ for MDI configuration and BI_DA+ for MDI-X configuration, respectively.                                            |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                                                                      |

|            |             |                     | TXRXP_B is the positive receive signal (RX+) for MDI configuration and the positive transmit signal (TX+) for MDI-X configuration, respectively. |

| 18         | TXRXM_B     | I/O                 | Media Dependent Interface[1], negative signal of differential pair                                                                               |

|            |             |                     | 1000Base-T Mode:                                                                                                                                 |

|            |             |                     | TXRXM_B corresponds to BI_DB- for MDI configuration and BI_DA- for MDI-X configuration, respectively.                                            |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                                                                      |

|            |             |                     | TXRXM_B is the negative receive signal (RX-) for MDI configuration and the negative transmit signal (TX-) for MDI-X configuration, respectively. |

| 19         | AGNDH       | Gnd                 | Analog ground                                                                                                                                    |

|            |             |                     |                                                                                                                                                  |

| Pin Number | Pin Name    | Type <sup>(1)</sup> | Pin Function                                                                                          |

|------------|-------------|---------------------|-------------------------------------------------------------------------------------------------------|

| 20         | TXRXP_C     | I/O                 | Media Dependent Interface[2], positive signal of differential pair                                    |

|            |             |                     | 1000Base-T Mode:                                                                                      |

|            |             |                     | TXRXP_C corresponds to BI_DC+ for MDI configuration and BI_DD+ for MDI-X configuration, respectively. |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                           |

|            |             |                     | TXRXP_C is not used.                                                                                  |

| 21         | TXRXM_C     | I/O                 | Media Dependent Interface[2], negative signal of differential pair                                    |

|            |             |                     | 1000Base-T Mode:                                                                                      |

|            |             |                     | TXRXM_C corresponds to BI_DC- for MDI configuration and BI_DD- for MDI-X configuration, respectively. |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                           |

|            |             |                     | TXRXM_C is not used.                                                                                  |

| 22         | AVDDH       | Р                   | 3.3V analog V <sub>DD</sub>                                                                           |

| 23         | AGNDH       | Gnd                 | Analog ground                                                                                         |

| 24         | AGNDL_ADC_C | Gnd                 | Analog ground                                                                                         |

| 25         | AVDDL       | Р                   | 1.2V analog V <sub>DD</sub>                                                                           |

| 26         | AVDDL       | Р                   | 1.2V analog V <sub>DD</sub>                                                                           |

| 27         | AGNDL_ADC_D | Gnd                 | Analog ground                                                                                         |

| 28         | AGNDH       | Gnd                 | Analog ground                                                                                         |

| 29         | AVDDH       | Р                   | 3.3V analog V <sub>DD</sub>                                                                           |

| 30         | TXRXP_D     | I/O                 | Media Dependent Interface[3], positive signal of differential pair                                    |

|            |             |                     | 1000Base-T Mode:                                                                                      |

|            |             |                     | TXRXP_D corresponds to BI_DD+ for MDI configuration and BI_DC+ for MDI-X configuration, respectively. |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                           |

|            |             |                     | TXRXP_D is not used.                                                                                  |

| 31         | TXRXM_D     | I/O                 | Media Dependent Interface[3], negative signal of differential pair                                    |

|            |             |                     | 1000Base-T Mode:                                                                                      |

|            |             |                     | TXRXM_D corresponds to BI_DD- for MDI configuration and BI_DC- for MDI-X configuration, respectively. |

|            |             |                     | 10Base-T / 100Base-TX Mode:                                                                           |

|            |             |                     | TXRXM_D is not used.                                                                                  |

| 32         | AVDDH       | Р                   | 3.3V analog V <sub>DD</sub>                                                                           |

| 33         | NC          | -                   | No connect                                                                                            |

| 34         | NC          | -                   | No connect                                                                                            |

| 35         | NC          | -                   | No connect                                                                                            |

| 36         | NC          | -                   | No connect                                                                                            |

| 37         | NC          | -                   | No connect                                                                                            |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

|            |             |                     |                                                                                                       |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Pin Function                                                                                     |              |                                                              |                    |

|------------|----------|---------------------|--------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------|--------------------|

| 38         | LED6     | I/O                 | LED Output: Programmable                                                                         | e LED6 Outp  | out                                                          |                    |

|            |          |                     | The LED6 pin is programmed via register 11h bits [7:6], LED_SEL[1:0], and is defined as follows. |              |                                                              |                    |

|            |          |                     |                                                                                                  |              | guration (default)                                           |                    |

|            |          |                     |                                                                                                  | 5-LED Confi  | guration                                                     | 1                  |

|            |          |                     | 10Base-T Link                                                                                    | Pin State    | LED Definition                                               |                    |

|            |          |                     | Link off                                                                                         | Н            | OFF                                                          |                    |

|            |          |                     | Link on                                                                                          | L            | ON                                                           |                    |

|            |          |                     | LED_SEL[1:0] = (1,0) //                                                                          | 4-LED Confi  | guration                                                     |                    |

|            |          |                     | 10Base-T – Link / Activity                                                                       | Pin State    | LED Definition                                               |                    |

|            |          |                     | Link off                                                                                         | Н            | OFF                                                          |                    |

|            |          |                     | Link on                                                                                          | L            | ON                                                           |                    |

|            |          |                     | Activity (RX, TX)                                                                                | Toggle       | Blinking                                                     |                    |

|            |          |                     | Activity (IVX, IX)                                                                               | roggie       | Billiking                                                    |                    |

|            |          |                     | LED_SEL[1:0] = (0,0) //                                                                          | Reserved –   | not used                                                     |                    |

| 39         | DVDDL    | Р                   | 1.2V digital V <sub>DD</sub>                                                                     |              |                                                              |                    |

| 40         | VSS      | Gnd                 | Digital ground                                                                                   |              |                                                              |                    |

| 41         | VSS      | Gnd                 | Digital ground                                                                                   |              |                                                              |                    |

| 42         | LED5 /   | I/O                 | LED Output: Programmable LED5 Output /                                                           |              |                                                              |                    |

|            | PHYAD4   |                     |                                                                                                  | set. See "St | ue is latched as PHY rapping Options" se hoits [7:6], LED_SE | ction for details. |

|            |          |                     | LED_SEL[1:0] = (1,1) //                                                                          | 6-LED Confi  | guration (default)                                           |                    |

|            |          |                     | LED_SEL[1:0] = (0,1) //                                                                          | 5-LED Confi  | guration                                                     |                    |

|            |          |                     | 100Base-T Link                                                                                   | Pin State    | LED Definition                                               |                    |

|            |          |                     | Link off                                                                                         | Н            | OFF                                                          |                    |

|            |          |                     | Link on                                                                                          | L            | ON                                                           |                    |

|            |          |                     | LED_SEL[1:0] = (1,0) //                                                                          | 4-LED Confi  | guration                                                     |                    |

|            |          |                     | 100Base-T – Link / Activity                                                                      | Pin State    | LED Definition                                               |                    |

|            |          |                     | Link off                                                                                         | Н            | OFF                                                          |                    |

|            |          |                     | Link on                                                                                          | L            | ON                                                           |                    |

|            |          |                     | Activity (RX, TX)                                                                                | Toggle       | Blinking                                                     |                    |

|            |          |                     | LED_SEL[1:0] = (0,0) //                                                                          | Reserved –   | not used                                                     |                    |

|            |          |                     |                                                                                                  |              |                                                              |                    |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Pin Function                                                                                                                           |               |                      |                 |  |

|------------|----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|-----------------|--|

| 43         | LED4 /   | I/O                 | LED Output: Programmable                                                                                                               | e LED4 Outp   | out /                |                 |  |

|            | PHYAD3   |                     | Config Mode: The pull-up/pull-down value is latched as PHYADD[3] during power-up / reset. See "Strapping Options" section for details. |               |                      |                 |  |

|            |          |                     | The LED4 pin is programmed via defined as follows.                                                                                     | a register 11 | h bits [7:6], LED_SE | EL[1:0], and is |  |

|            |          |                     | LED_SEL[1:0] = (1,1) // 6                                                                                                              | 6-LED Confi   | guration (default)   |                 |  |

|            |          |                     | LED_SEL[1:0] = (0,1) // 5                                                                                                              | 5-LED Confi   | guration             |                 |  |

|            |          |                     | 1000Base-T Link                                                                                                                        | Pin State     | LED Definition       |                 |  |

|            |          |                     | Link off                                                                                                                               | Н             | OFF                  |                 |  |

|            |          |                     | Link on                                                                                                                                | L             | ON                   |                 |  |

|            |          |                     | LED_SEL[1:0] = (1,0) // 4                                                                                                              | 4-LED Confi   | guration             |                 |  |

|            |          |                     | 1000Base-T – Link / Activity                                                                                                           | Pin State     | LED Definition       |                 |  |

|            |          |                     | Link off                                                                                                                               | Н             | OFF                  |                 |  |

|            |          |                     | Link on                                                                                                                                | L             | ON                   |                 |  |

|            |          |                     | Activity (RX, TX)                                                                                                                      | Toggle        | Blinking             |                 |  |

|            |          |                     |                                                                                                                                        |               | _                    |                 |  |

|            |          |                     | LED_SEL[1:0] = (0,0) // F                                                                                                              | Reserved –    | not used             |                 |  |

| 44         | LED3 /   | I/O                 | LED Output: Programmable                                                                                                               | E LED3 Outp   | out /                |                 |  |

|            | PHYAD2   |                     | Config Mode: The pull-up/pull-down value is latched as PHYADD[2] during power-up / reset. See "Strapping Options" section for details. |               |                      |                 |  |

|            |          |                     | • .                                                                                                                                    |               |                      |                 |  |

|            |          |                     | The LED3 pin is programmed via register 11h bits [7:6], LED_SEL[1:0], and is defined as follows.                                       |               |                      |                 |  |

|            |          |                     | LED CELIA-01 (4.4) // //                                                                                                               | S LED Confi   |                      |                 |  |

|            |          |                     | LED_SEL[1:0] = (1,1)  // 6-LED Configuration (default) LED_SEL[1:0] = (0,1)  // 5-LED Configuration                                    |               |                      |                 |  |

|            |          |                     |                                                                                                                                        | 1-LED Confi   | -                    |                 |  |

|            |          |                     | Duplex / Collision                                                                                                                     | Pin State     | LED Definition       | ]               |  |

|            |          |                     | Half Duplex                                                                                                                            | Н             | OFF                  |                 |  |

|            |          |                     | Full Duplex                                                                                                                            | L             | ON                   |                 |  |

|            |          |                     | Collision                                                                                                                              | Toggle        | Blinking             |                 |  |

|            |          |                     |                                                                                                                                        |               | <del>-</del>         | 1               |  |

|            |          |                     | LED_SEL[1:0] = (0,0) // F                                                                                                              | Reserved –    | not used             |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

|            |          |                     |                                                                                                                                        |               |                      |                 |  |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Pin Function                                                                                                                                                                                                                             |  |  |  |

|------------|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 45         | LED2 /   | I/O                 | LED Output: Programmable LED2 Output /                                                                                                                                                                                                   |  |  |  |

|            | PHYAD1   |                     | Config Mode: The pull-up/pull-down value is latched as PHYADD[1] during power-up / reset. See "Strapping Options" section for details.                                                                                                   |  |  |  |

|            |          |                     | The LED2 pin is programmed via register 11h bits [7:6], LED_SEL[1:0], and is defined as follows.                                                                                                                                         |  |  |  |

|            |          |                     | LED_SEL[1:0] = (1,1) // 6-LED Configuration (default)                                                                                                                                                                                    |  |  |  |

|            |          |                     | Receive Activity Pin State LED Definition                                                                                                                                                                                                |  |  |  |

|            |          |                     | No Receive Activity H OFF                                                                                                                                                                                                                |  |  |  |

|            |          |                     | Receive Activity L, Toggle ON, Blinking                                                                                                                                                                                                  |  |  |  |

|            |          |                     | LED_SEL[1:0] = (0,1) // Reserved – not used  LED2 pin is internally pulled high.                                                                                                                                                         |  |  |  |

|            |          |                     | LED_SEL[1:0] = (1,0) // Reserved – not used  LED2 pin is internally pulled high.                                                                                                                                                         |  |  |  |

|            |          |                     | LED_SEL[1:0] = (0,0)  // Reserved – not used                                                                                                                                                                                             |  |  |  |

| 46         | DVDDH    | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                                                                                             |  |  |  |

| 47         | VSSPST   | Gnd                 | Digital ground                                                                                                                                                                                                                           |  |  |  |

| 48         | LED1/    | I/O                 | LED Output: Programmable LED1 Output /                                                                                                                                                                                                   |  |  |  |

|            |          |                     | Config Mode: The pull-up/pull-down value is latched as PHYADD[0] during power-up / reset. See "Strapping Options" section for details.  The LED1 pin is programmed via register 11h bits [7:6], LED_SEL[1:0], and is defined as follows. |  |  |  |

|            |          |                     | LED_SEL[1:0] = (1,1) // 6-LED Configuration (default)                                                                                                                                                                                    |  |  |  |

|            |          |                     | Transmit Activity Pin State LED Definition                                                                                                                                                                                               |  |  |  |

|            |          |                     | No Transmit Activity H OFF                                                                                                                                                                                                               |  |  |  |

|            |          |                     | Transmit Activity L, Toggle ON, Blinking                                                                                                                                                                                                 |  |  |  |

|            |          |                     | LED_SEL[1:0] = (0,1)  // 5-LED Configuration                                                                                                                                                                                             |  |  |  |

|            |          |                     | Receive/Transmit Activity Pin State LED Definition                                                                                                                                                                                       |  |  |  |

|            |          |                     | No Receive/Transmit Activity H OFF                                                                                                                                                                                                       |  |  |  |

|            |          |                     | Receive/Transmit Activity L, Toggle ON, Blinking                                                                                                                                                                                         |  |  |  |

|            |          |                     | LED_SEL[1:0] = (1,0) // Reserved – not used                                                                                                                                                                                              |  |  |  |

|            |          |                     | LED1 pin is internally pulled high.                                                                                                                                                                                                      |  |  |  |

|            |          |                     | LED1 pin is internally pulled high.  LED_SEL[1:0] = (0,0) // Reserved – not used                                                                                                                                                         |  |  |  |

| 49         | DVDDL    | P                   |                                                                                                                                                                                                                                          |  |  |  |

| Pin Number | Pin Name  | Type <sup>(1)</sup> | Pin Function                   |                                                                |

|------------|-----------|---------------------|--------------------------------|----------------------------------------------------------------|

| 51         | TXD0      | I                   | GMII Mode:                     | GMII TXD0 (Transmit Data 0) Input                              |

|            |           |                     | MII Mode:                      | MII TXD0 (Transmit Data 0) Input                               |

| 52         | TXD1      | I                   | GMII Mode:                     | GMII TXD1 (Transmit Data 1) Input                              |

|            |           |                     | MII Mode:                      | MII TXD1 (Transmit Data 1) Input                               |

| 53         | TXD2      | I                   | GMII Mode:                     | GMII TXD2 (Transmit Data 2) Input                              |

|            |           |                     | MII Mode:                      | MII TXD2 (Transmit Data 2) Input                               |

| 54         | TXD3      | 1                   | GMII Mode:                     | GMII TXD3 (Transmit Data 3) Input                              |

|            |           |                     | MII Mode:                      | MII TXD3 (Transmit Data 3) Input                               |

| 55         | VSS       | Gnd                 | Digital ground                 |                                                                |

| 56         | DVDDL     | Р                   | 1.2V digital V <sub>DD</sub>   |                                                                |

| 57         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>   |                                                                |

| 58         | TXD4      | I                   | GMII Mode:                     | GMII TXD4 (Transmit Data 4) Input                              |

|            |           |                     | MII Mode:                      | This pin is not used and can be driven high or low.            |

| 59         | TXD5      | I                   | GMII Mode:                     | GMII TXD5 (Transmit Data 5) Input                              |

|            |           |                     | MII Mode:                      | This pin is not used and can be driven high or low.            |

| 60         | TXD6      | I                   | GMII Mode:                     | GMII TXD6 (Transmit Data 6) Input                              |

|            |           |                     | MII Mode:                      | This pin is not used and can be driven high or low.            |

| 61         | TXD7      | 1                   | GMII Mode:                     | GMII TXD7 (Transmit Data 7) Input                              |

|            |           |                     | MII Mode:                      | This pin is not used and can be driven high or low.            |

| 62         | VSSPST    | Gnd                 | Digital ground                 |                                                                |

| 63         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>   |                                                                |

| 64         | TX_ER     | 1                   | GMII Mode:                     | GMII TX_ER (Transmit Error) Input                              |

|            |           |                     | MII Mode:                      | MII TX_ER (Transmit Error) Input                               |

|            |           |                     | If GMII / MII MAC<br>tied low. | C does not provide the TX_ER output signal, this pin should be |

| 65         | GTX_CLK / | I/O                 | GMII Mode:                     | GMII GTX_CLK (Transmit Reference Clock) Input /                |

|            | TX_CLK    |                     | MII Mode:                      | MII TX_CLK (Transmit Reference Clock) Output                   |

| 66         | VSSPST    | Gnd                 | Digital ground                 |                                                                |

| 67         | TX_EN     | I                   | GMII Mode:                     | GMII TX_EN (Transmit Enable) Input                             |

|            | _         |                     | MII Mode:                      | MII TX_EN (Transmit Enable) Input                              |

| 68         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>   |                                                                |

| 69         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>   |                                                                |

| 70         | RXD7      | 0                   | GMII Mode:                     | GMII RXD7 (Receive Data 7) Output                              |

|            |           |                     | MII Mode:                      | This pin is not used and is driven low.                        |

| 71         | VSS       | Gnd                 | Digital ground                 |                                                                |

| 72         | VSS       | Gnd                 | Digital ground                 |                                                                |

| 73         | RXD6      | 0                   | GMII Mode:                     | GMII RXD6 (Receive Data 6) Output                              |

|            |           |                     | MII Mode:                      | This pin is not used and is driven low.                        |

| 74         | DVDDL     | Р                   | 1.2V digital V <sub>DD</sub>   |                                                                |

| 75         | DVDDL     | Р                   | 1.2V digital V <sub>DD</sub>   |                                                                |

| 76         | RXD5      | 0                   | GMII Mode:                     | GMII RXD5 (Receive Data 5) Output                              |

|            |           |                     | MII Mode:                      | This pin is not used and is driven low.                        |

|            |           |                     |                                |                                                                |

| Pin Number | Pin Name  | Type <sup>(1)</sup> | Pin Function                                                                                                                                                |                                                                                                                       |  |

|------------|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 77         | RXD4      | 0                   | GMII Mode:                                                                                                                                                  | GMII RXD4 (Receive Data 4) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | This pin is not used and is driven low.                                                                               |  |

| 78         | RXD3 /    | I/O                 | GMII Mode:                                                                                                                                                  | GMII RXD3 (Receive Data 3) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RXD3 (Receive Data 3) Output /                                                                                    |  |

|            | MODE3     |                     | Config Mode: The pull-up/pull-down value is latched as MODE3 during power-up / reset. See "Strapping Options" section for details.                          |                                                                                                                       |  |

| 79         | VSSPST    | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 80         | VSSPST    | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 81         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                |                                                                                                                       |  |

| 82         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                |                                                                                                                       |  |

| 83         | RXD2/     | I/O                 | GMII Mode:                                                                                                                                                  | GMII RXD2 (Receive Data 2) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RXD2 (Receive Data 2) Output) /                                                                                   |  |

|            | MODE2     |                     | Config Mode:                                                                                                                                                | The pull-up/pull-down value is latched as MODE2 during power-up / reset. See "Strapping Options" section for details. |  |

| 84         | VSS       | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 85         | VSS       | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 86         | DVDDL     | Р                   | 1.2V digital V <sub>DD</sub>                                                                                                                                |                                                                                                                       |  |

| 87         | DVDDL     | Р                   | 1.2V digital V <sub>DD</sub>                                                                                                                                |                                                                                                                       |  |

| 88         | RXD1 /    | I/O                 | GMII Mode:                                                                                                                                                  | GMII RXD1 (Receive Data 1) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RXD1 (Receive Data 1) Output /                                                                                    |  |

|            | MODE1     |                     | Config Mode:                                                                                                                                                | The pull-up/pull-down value is latched as MODE1 during power-up / reset. See "Strapping Options" section for details. |  |

| 89         | RXD0 /    | I/O                 | GMII Mode:                                                                                                                                                  | GMII RXD0 (Receive Data 0) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RXD0 (Receive Data 0) Output /                                                                                    |  |

|            | MODE0     |                     | Config Mode:                                                                                                                                                | The pull-up/pull-down value is latched as MODE0 during power-up / reset. See "Strapping Options" section for details. |  |

| 90         | RX_DV /   | I/O                 | GMII Mode:                                                                                                                                                  | GMII RX_DV (Receive Data Valid) Output                                                                                |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RX_DV (Receive Data Valid) Output /                                                                               |  |

|            | CLK125_EN |                     | Config Mode:                                                                                                                                                | Latched as CLK125_NDO Output Enable during power-up / reset. See "Strapping Options" section for details.             |  |

| 91         | VSSPST    | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 92         | DVDDH     | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                |                                                                                                                       |  |

| 93         | RX_ER     | 0                   | GMII Mode:                                                                                                                                                  | GMII RX_ER (Receive Error) Output                                                                                     |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RX_ER (Receive Error) Output                                                                                      |  |

| 94         | RX_CLK    | 0                   | GMII Mode:                                                                                                                                                  | GMII RX_CLK (Receive Reference Clock) Output                                                                          |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII RX_CLK (Receive Reference Clock) Output                                                                           |  |

| 95         | VSSPST    | Gnd                 | Digital ground                                                                                                                                              |                                                                                                                       |  |

| 96         | CRS       | 0                   | GMII Mode:                                                                                                                                                  | GMII CRS (Carrier Sense) Output                                                                                       |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII CRS (Carrier Sense) Output                                                                                        |  |

| 97         | MDC       | lpu                 | Management Data Clock Input                                                                                                                                 |                                                                                                                       |  |

|            |           |                     | This pin is the input reference clock for MDIO (pin 98).                                                                                                    |                                                                                                                       |  |

| 98         | MDIO      | Ipu/O               | Management Data Input / Output                                                                                                                              |                                                                                                                       |  |

|            |           |                     | This pin is synchronous to MDC (pin 97) and requires an external pull-up resistor to 3.3V digital $V_{DD}$ in a range from $1.0 K\Omega$ to $4.7 K\Omega$ . |                                                                                                                       |  |

| 99         | COL       | 0                   | GMII Mode:                                                                                                                                                  | GMII COL (Collision Detected) Output                                                                                  |  |

|            |           |                     | MII Mode:                                                                                                                                                   | MII COL (Collision Detected) Output                                                                                   |  |

| Pin Number | Pin Name   | Type <sup>(1)</sup> | Pin Function                                                                                                                                                                                                           |  |

|------------|------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 100        | DVDDH      | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                                                                           |  |

| 101        | INT_N      | 0                   | Interrupt Output                                                                                                                                                                                                       |  |

|            |            |                     | This pin provides a programmable interrupt output and requires an external pull-up resistor to 3.3V digital $V_{DD}$ in a range from $1.0 \text{K}\Omega$ to $4.7 \text{K}\Omega$ when active low.                     |  |

|            |            |                     | Register 1Bh is the Interrupt Control/Status Register for programming the interrupt conditions and reading the interrupt status. Register 1Fh bit 14 sets the interrupt output to active low (default) or active high. |  |

| 102        | VSS        | Gnd                 | Digital ground                                                                                                                                                                                                         |  |

| 103        | DVDDL      | Р                   | 1.2V digital V <sub>DD</sub>                                                                                                                                                                                           |  |

| 104        | VSS        | Gnd                 | Digital ground                                                                                                                                                                                                         |  |

| 105        | DVDDL      | Р                   | 1.2V digital V <sub>DD</sub>                                                                                                                                                                                           |  |

| 106        | DVDDH      | Р                   | 3.3V digital V <sub>DD</sub>                                                                                                                                                                                           |  |

| 107        | CLK125 NDO | 0                   | 125MHz Clock Output                                                                                                                                                                                                    |  |

|            | _          |                     | This pin provides a 125MHz reference clock output option for use by the MAC.                                                                                                                                           |  |

| 108        | VSSPST     | Gnd                 | Digital ground                                                                                                                                                                                                         |  |

| 109        | VSSPST     | Gnd                 | Digital ground                                                                                                                                                                                                         |  |

| 110        | RESET_N    | lpu                 | Chip Reset (active low)                                                                                                                                                                                                |  |

|            | _          |                     | Hardware pin configurations are strapped-in at the de-assertion (rising edge) of RESET_N. See "Strapping Options" section for more details.                                                                            |  |

| 111        | NC         | -                   | No connect                                                                                                                                                                                                             |  |

| 112        | NC         | -                   | No connect                                                                                                                                                                                                             |  |

| 113        | VSS        | Gnd                 | Digital ground                                                                                                                                                                                                         |  |