### **General Description**

The MAX9140/MAX9141 are single and the MAX9142/ MAX9144 are dual/quad high-speed comparators optimized for systems powered from a 3V or 5V supply. The MAX9141 features latch enable and device shutdown. These devices combine high speed, low power, and Rail-to-Rail<sup>®</sup> inputs. Propagation delay is 40ns, while supply current is only 150µA per comparator.

The input common-mode range of the MAX9140/ MAX9141/MAX9142/MAX9144 extends beyond both power-supply rails. The outputs pull to within 0.3V of either supply rail without external pullup circuitry, making these devices ideal for interface with both CMOS and TTL logic. All input and output pins can tolerate a continuous short-circuit fault condition to either rail. Internal hysteresis ensures clean output switching, even with slow-moving input signals.

The MAX9140/MAX9141/MAX9142/MAX9144 are higher-speed, lower-power, and lower-cost upgrades to industry-standard comparators MAX941/MAX942/ MAX944.

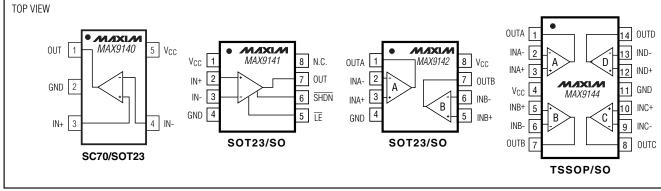

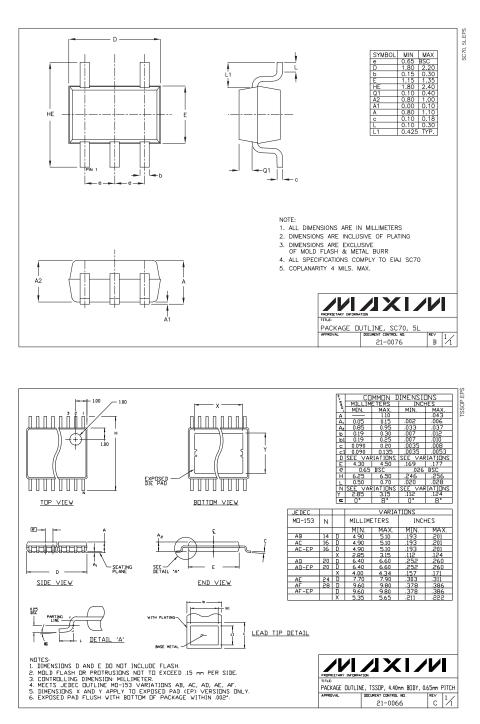

The MAX9140 are offered in tiny 5-pin SC70 and SOT23 packages. The MAX9141 and MAX9142 are available in 8-pin SOT23 and SO packages, while the MAX9144 is available in both 14-pin SO and TSSOP packages.

#### Applications

Line Receivers

Battery-Powered Systems

Threshold Detectors/Discriminators

3V/5V Systems

Zero-Crossing Detectors

Sampling Circuits

#### Features

- Fast, 40ns Propagation Delay (10mV Overdrive)

- Low Power: 0.45mW Power Dissipation Per Comparator (3V) 150µA Supply Current

- Optimized for 3V and 5V Applications (Operation Down to 2.7V)

- ♦ Rail-to-Rail Input Voltage Range

- ◆ Low, 500µV Offset Voltage

- Internal Hysteresis for Clean Switching

- Outputs Swing 300mV of Power Rails

- ♦ CMOS/TTL-Compatible Outputs

- Output Latch (MAX9141 only)

- Shutdown Function (MAX9141 only)

- ♦ Available in SC70 and SOT23 Packages

### \_Ordering Information

| PART                 | TEMP.<br>RANGE | PIN-<br>PACKAGE | TOP<br>MARK |

|----------------------|----------------|-----------------|-------------|

| <b>MAX9140</b> EXK-T | -40°C to +85°C | 5 SC70-5        | ACC         |

| MAX9140EUK-T         | -40°C to +85°C | 5 SOT23-5       | ADQP        |

| MAX9141EKA-T         | -40°C to +85°C | 8 SOT23-8       | AAFD        |

| MAX9141ESA           | -40°C to +85°C | 8 SO            | _           |

| MAX9142EKA-T         | -40°C to +85°C | 8 SOT23-8       | AAFE        |

| MAX9142ESA           | -40°C to +85°C | 8 SO            | —           |

| MAX9144EUD           | -40°C to +85°C | 14 TSSOP        | _           |

| MAX9144ESD           | -40°C to +85°C | 14 SO           |             |

## Pin Configurations

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

Power Supply Ranges

| and capping hangee                                                |

|-------------------------------------------------------------------|

| Supply Voltage (VCC to GND)+6V                                    |

| Differential Input Voltage0.3V to (V <sub>CC</sub> + 0.3V)        |

| Common-Mode Input Voltage to GND0.3V to (V <sub>CC</sub> + 0.3V)  |

| LE Input Voltage (MAX9141 only)0.3V to (V <sub>CC</sub> + 0.3V)   |

| SHDN Input Voltage (MAX9141 only)0.3V to (V <sub>CC</sub> + 0.3V) |

| Input/Output Short-Circuit Duration to                            |

| V <sub>CC</sub> or GNDContinuous                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 5-Pin SC70 (derate 3.1mW/°C above +70°C)247mW         |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW        |

| 8-Pin SOT23 (derate 9.1mW/°C above +70°C)727mW        |

| 8-Pin SO (derate 5.9mW/°C above +70°C)470.6mW         |

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C)727mW       |

| 14-Pin SO (derate 8.33mW/°C above +70°C)666.7mW       |

| Operating Temperature Range40°C to +85°C              |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V, V_{CM} = 0, \overline{SHDN} = \overline{LE} = V_{CC}$  (MAX9141 only),  $C_L = 15pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                       | SYMBOL                                 | CO                                                                                | MIN                          | ТҮР                      | MAX                         | UNITS                 |      |

|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------------|------------------------------|--------------------------|-----------------------------|-----------------------|------|

| Operating Supply Voltage        | V <sub>CC</sub>                        | (Note 2)                                                                          |                              | 2.7                      |                             | 5.5                   | V    |

| Input Voltage Range             | V <sub>CMR</sub>                       | (Note 3)                                                                          |                              | -0.2                     |                             | V <sub>CC</sub> + 0.2 | V    |

| Input Offert Veltage            | V <sub>OS</sub>                        | (Note 4)                                                                          | $T_A = +25^{\circ}C$         |                          | 0.5                         | 2                     | mV   |

| Input Offset Voltage            |                                        | (Note 4)                                                                          | $T_A = T_{MIN}$ to $T_{MAX}$ |                          |                             | 4.5                   |      |

| Input Hysteresis                | VHYST                                  | (Note 5)                                                                          |                              |                          | 1.5                         |                       | mV   |

| Input Bias Current              | Ι <sub>Β</sub>                         | (Note 6)                                                                          |                              |                          | 90                          | 320                   | nA   |

| Input Offset Current            | los                                    |                                                                                   |                              |                          | 8                           | 120                   | nA   |

| Common-Mode Rejection Ratio     | CMRR                                   | $V_{CC} = 5.5V$ (Note 7                                                           | 7)                           |                          | 80                          | 800                   | μV/V |

| Power-Supply Rejection Ratio    | PSRR                                   | $2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V}$                        |                              |                          | 80                          | 750                   | μV/V |

| Output High Voltage             | V <sub>OH</sub>                        | ISOURCE = 4mA                                                                     | V <sub>CC</sub> -<br>0.425   | V <sub>CC</sub> -<br>0.3 |                             | V                     |      |

| Output Low Voltage              | V <sub>OL</sub>                        | I <sub>SINK</sub> = 4mA                                                           |                              | 0.3                      | 0.425                       | V                     |      |

| Output Leakage Current          | ILEAK                                  | SHDN = GND, MA                                                                    |                              | 0.04                     | 1                           | μA                    |      |

| Supply Current (Per Comparator) | Icc                                    | $V_{CM} = V_{CC} = 3V$                                                            | MAX9141                      |                          | 165                         | 275                   | μΑ   |

|                                 |                                        |                                                                                   | MAX9140/MAX9142/<br>MAX9144  |                          | 150                         | 250                   |      |

|                                 |                                        | $V_{CM} = V_{CC} = 5V$                                                            | MAX9141                      |                          | 200                         | 320                   |      |

|                                 |                                        |                                                                                   | MAX9140/MAX9142/<br>MAX9144  |                          | 165                         | 300                   |      |

|                                 |                                        | MAX9141 only, $\overline{SHDN} = GND$ ;<br>V <sub>CC</sub> = V <sub>CM</sub> = 3V |                              |                          | 12                          | 30                    |      |

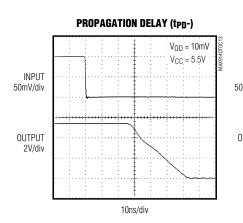

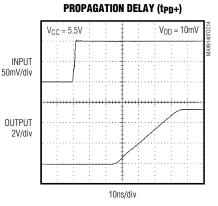

| Propagation Delay               | t <sub>PD+</sub> ,<br>t <sub>PD-</sub> | $V_{CC} = 3V, V_{OD} = 10mV$                                                      |                              |                          | 40                          |                       | ns   |

| Differential Propagation Delay  | dt <sub>PD</sub>                       | V <sub>OD</sub> = 10mV (Note 9)                                                   |                              |                          | 2                           |                       | ns   |

| Propagation Delay Skew          |                                        | V <sub>OD</sub> = 10mV (Note 10)                                                  |                              |                          | 2                           |                       | ns   |

| Logic Input Voltage High        | VIH                                    | (Note 11)                                                                         | V <sub>CC</sub> /2 + 0.4     | V <sub>CC</sub> /2       |                             | V                     |      |

| Logic Input Voltage Low         | VIL                                    | (Note 11)                                                                         |                              | V <sub>CC</sub> /2       | V <sub>CC</sub> /2 -<br>0.4 | V                     |      |

| Logic Input Current             | I <sub>IL</sub> , I <sub>IH</sub>      | VLOGIC = 0 to VCC                                                                 |                              | 2                        | 10                          | μA                    |      |

#### ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 5V, V_{CM} = 0, \overline{SHDN} = \overline{LE} = V_{CC}$  (MAX9141 only),  $C_L = 15pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                | SYMBOL         | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|--------------------------|----------------|------------|-----|-----|-----|-------|

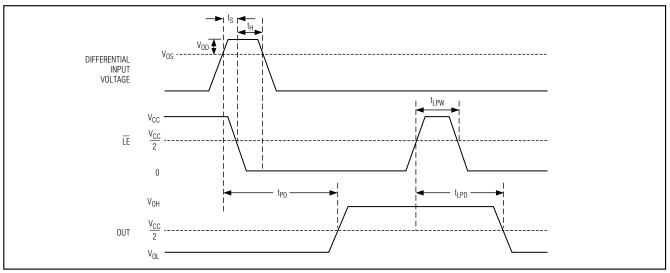

| Data-to-Latch Setup Time | ts             | (Note 12)  |     | 16  |     | ns    |

| Latch-to-Data Hold Time  | t <sub>H</sub> | (Note 12)  |     | 16  |     | ns    |

| Latch Pulse Width        | tLPW           | (Note 12)  |     | 45  |     | ns    |

| Latch Propagation Delay  | tlpd           | (Note 12)  |     | 60  |     | ns    |

| Shutdown Enable Time     |                | (Note 13)  |     | 1   |     | μs    |

| Shutdown Disable Time    |                | (Note 13)  |     | 5   |     | μs    |

All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design. Note 1:

Note 2: Inferred from PSRR test.

Inferred from CMRR test. Note also that either or both inputs can be driven to the absolute maximum limit (0.3V beyond either Note 3: supply rail) without damage or false output inversion.

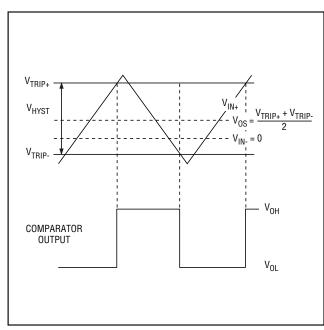

Note 4: V<sub>OS</sub> is defined as the center of the input-referred hysteresis zone. See Figure 1.

The input-referred trip points are the extremities of the differential input voltage required to make the comparator output Note 5: change state. The difference between the upper and lower trip points is equal to the width of the input-referred hysteresis zone. See Figure 1.

- Note 6: The polarity of IB reverses direction as V<sub>CM</sub> approaches either supply rail.

- Note 7: Specified over the full common-mode voltage range (V<sub>CMR</sub>).

Note 8: Specification is for current flowing into or out of the output pin for V<sub>OUT</sub> driven to any voltage from V<sub>CC</sub> to GND while the part is in shutdown.

- Specified between any two channels in the MAX9142/MAX9144. Note 9:

- Note 10: Specified as the difference between  $t_{PD+}$  and  $t_{PD-}$  for any one comparator.

- Note 11: Applies to the MAX9141 only for both SHDN and LE.

- Note 12: Applies to the MAX9141 only. Comparator is active with  $\overline{LE}$  driven high and is latched with  $\overline{LE}$  driven low (V<sub>OD</sub> = 10mV). See Figure 2.

- Note 13: Applicable to the MAX9141 only. Comparator is active with the SHDN driven high and is shutdown with SHDN driven low. Shutdown enable time is the delay when the SHDN is driven high to the time the output is valid. Shutdown disable time is the delay when the SHDN is driven low to the time the comparator shuts down.

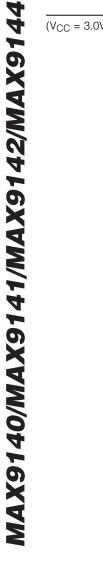

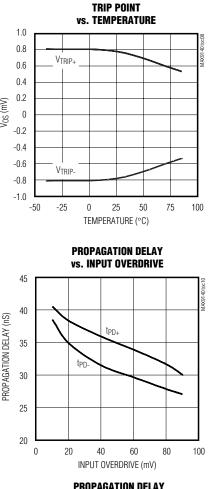

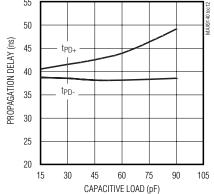

#### $(V_{CC} = 3.0V, V_{CM} = 0, C_L = 15pF, V_{OD} = 10mV, T_A = +25^{\circ}C, unless otherwise noted.)$

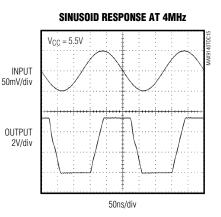

**Typical Operating Characteristics**

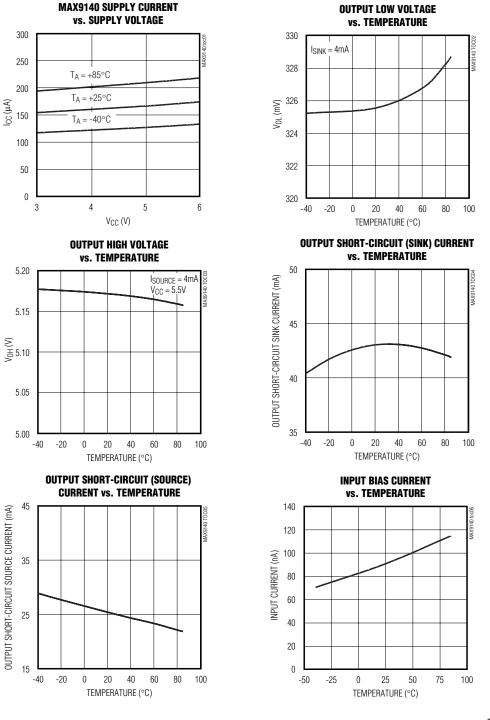

#### Typical Operating Characteristics (continued)

(V<sub>CC</sub> = 3.0V, V<sub>CM</sub> = 0, C<sub>L</sub> =15pF, V<sub>OD</sub> = 10mV, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### PROPAGATION DELAY vs. capacitive load

MAX9140/MAX9141/MAX9142/MAX9144

M/IXI/M

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 3.0V, V<sub>CM</sub> = 0, C<sub>L</sub> =15pF, V<sub>OD</sub> = 10mV, T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Pin Description**

| PIN     |         |         |         | NAME    | FUNCTION                                                                                                                |  |  |

|---------|---------|---------|---------|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX9140 | MAX9141 | MAX9142 | MAX9144 | INAIVIE | FUNCTION                                                                                                                |  |  |

| _       | _       | 1       | 1       | OUTA    | Comparator A Output                                                                                                     |  |  |

|         |         | 2       | 2       | INA-    | Comparator A Inverting Input                                                                                            |  |  |

| _       | _       | 3       | 3       | INA+    | Comparator A Noninverting Input                                                                                         |  |  |

| 5       | 1       | 8       | 4       | Vcc     | Positive Supply                                                                                                         |  |  |

|         |         | 5       | 5       | INB+    | Comparator B Noninverting Input                                                                                         |  |  |

|         |         | 6       | 6       | INB-    | Comparator B Inverting Input                                                                                            |  |  |

|         |         | 7       | 7       | OUTB    | Comparator B Output                                                                                                     |  |  |

|         |         | _       | 8       | OUTC    | Comparator C Output                                                                                                     |  |  |

|         | _       | _       | 9       | INC-    | Comparator C Inverting Input                                                                                            |  |  |

|         |         | _       | 10      | INC+    | Comparator C Noninverting Input                                                                                         |  |  |

| 2       | 4       | 4       | 11      | GND     | Ground                                                                                                                  |  |  |

|         |         | _       | 12      | IND+    | Comparator D Noninverting Input                                                                                         |  |  |

|         | _       | _       | 13      | IND-    | Comparator D Inverting Input                                                                                            |  |  |

|         | _       | _       | 14      | OUTD    | Comparator D Output                                                                                                     |  |  |

| 3       | 2       | _       | —       | IN+     | Noninverting Input                                                                                                      |  |  |

| 4       | 3       | _       | —       | IN-     | Inverting Input                                                                                                         |  |  |

|         | 6       |         | _       | SHDN    | Shutdown: MAX9141 is active when SHDN is driven high;<br>MAX9141 is in shutdown when SHDN is driven low.                |  |  |

|         | 5       |         | _       | ĪĒ      | The output is latched when $\overline{\text{LE}}$ is low. The latch is transparent when $\overline{\text{LE}}$ is high. |  |  |

| 1       | 7       |         | —       | OUT     | Comparator Output                                                                                                       |  |  |

|         | 8       | _       | _       | N.C.    | No Connection. Not internally connected.                                                                                |  |  |

#### **Detailed Description**

The MAX9140/MAX9141/MAX9142/MAX9144 singlesupply comparators feature internal hysteresis, high speed, and low power. Their outputs are pulled to within 300mV of either supply rail without external pullup or pulldown circuitry. Rail-to-rail input voltage range and low-voltage single-supply operation make these devices ideal for portable equipment. The MAX9140/MAX9141/MAX9142/MAX9144 interface directly to CMOS and TTL logic.

Most high-speed comparators oscillate in the linear region because of noise or undesired parasitic feedback. This tends to occur when the voltage on one input is at or equal to the voltage on the other input. To counter the parasitic effects and noise, the MAX9140/ MAX9141/MAX9142/MAX9144 have an internal hysteresis of 1.5mV.

The hysteresis in a comparator creates two trip points: one for the rising input voltage and one for the falling input voltage (Figure 1). The difference between the trip points is the hysteresis. The average of the trip points is the offset voltage. When the comparator's input voltages are equal, the hysteresis effectively causes one comparator input voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. Standard comparators require hysteresis to be added with external resistors. The MAX9140/MAX9141/MAX9142/MAX9144's fixed internal hysteresis eliminates these resistors. To increase hysteresis and noise margin even more, add positive feedback with two resistors as a voltage divider from the output to the noninverting input.

Figure 1 illustrates the case where IN- is fixed and IN+ is varied. If the inputs were reversed, the figure would look the same, except the output would be inverted.

The MAX9141 includes an internal latch that allows storage of comparison results. The  $\overline{LE}$  pin has a high input impedance. If  $\overline{LE}$  is high, the latch is transparent (i.e., the comparator operates as though the latch is not present). The comparator's output state is latched when  $\overline{LE}$  is pulled low (Figure 2).

#### Shutdown Mode (MAX9141 Only)

The MAX9141 shuts down when the  $\overline{SHDN}$  pin is low. When shut down, the supply current drops to less than 12µA, and the three-state output becomes high impedance. The  $\overline{SHDN}$  pin has a high-input impedance. Connect  $\overline{SHDN}$  to V<sub>CC</sub> for normal operation. Exit shutdown with  $\overline{LE}$  high (transparent state); otherwise, the output will be indeterminate.

Figure 1. Input and Output Waveform, Noninverting Input Varied

#### Input Stage Circuitry

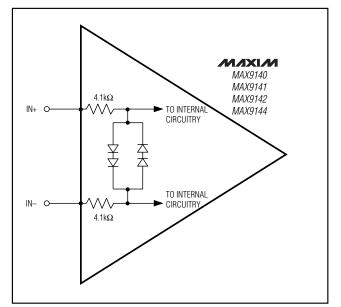

The MAX9140/MAX9141/MAX9142/MAX9144 include internal protection circuitry that prevents damage to the precision input stage from large differential input voltages. This protection circuitry consists of two back-to-back diodes between IN+ and IN- as well as two series 4.1k $\Omega$  resistors (Figure 3). The diodes limit the differential voltage applied to the internal circuitry of the comparators to be no more than 2V<sub>F</sub>, where V<sub>F</sub> is the forward voltage drop of the diode (about 0.7V at +25°C).

For a large differential input voltage (exceeding  $2V_F$ ), this protection circuitry increases the input bias current at IN+ (source) and IN- (sink).

Input Current =

$$\frac{(IN+ - IN-) - 2V_F}{2 \times 4.1 k\Omega}$$

Input current with large differential input voltages should not be confused with input bias current (IB). As long as the differential input voltage is less than  $2V_{F}$ , this input current is equal to IB. The output is in the correct logic state if one or both inputs are within the common-mode range.

Figure 2. MAX9141 Timing Diagram with Latch Operator

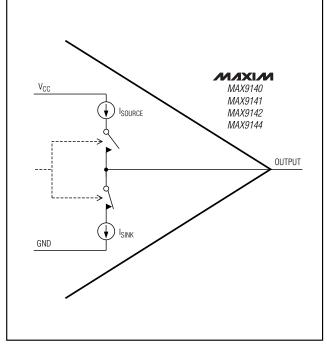

#### **Output Stage Circuitry**

The MAX9140/MAX9141/MAX9142/MAX9144 contain a current-driven output stage as shown in Figure 4. During an output transition, I<sub>SOURCE</sub> or I<sub>SINK</sub> is pushed or pulled to the output pin. The output source or sink current is high during the transition, creating a rapid slew rate. Once the output voltage reaches V<sub>OH</sub> or V<sub>OL</sub>, the source or sink current decreases to a small value, capable of maintaining the V<sub>OH</sub> or V<sub>OL</sub> static condition. This significant decrease in current conserves power after an output transition has occurred.

One consequence of a current-driven output stage is a linear dependence between the slew rate and the load capacitance. A heavy capacitive load will slow down a voltage output transition. This can be useful in noisesensitive applications where fast edges may cause interference.

#### **Applications Information**

#### **Circuit Layout and Bypassing**

The high-gain bandwidth of the MAX9140/MAX9141/ MAX9142/MAX9144 requires design precautions to realize the full high-speed capabilities of these comparators. The recommended precautions are:

- 1) Use a printed circuit board with a good, unbroken, low-inductance ground plane.

- 2) Place a decoupling capacitor (a 0.1 $\mu$ F ceramic capacitor is a good choice) as close to V<sub>CC</sub> as possible.

Figure 3. Input Stage Circuitry

- Pay close attention to the decoupling capacitor's bandwidth, keeping leads short.

- On the inputs and outputs, keep lead lengths short to avoid unwanted parasitic feedback around the comparators.

- 5) Solder the device directly to the printed circuit board instead of using a socket.

Figure 4. Output Stage Circuitry

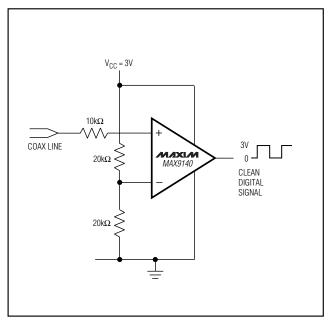

Figure 6. Line Receiver Application

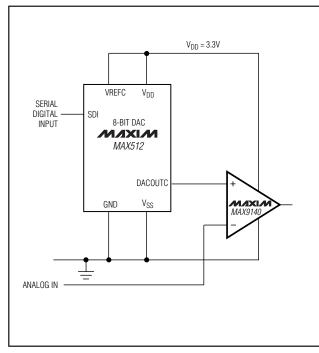

Figure 5. 3.3V Digitally Controlled Threshold Detector

#### \_Chip Information

| MAX9140 TRANSISTOR COUNT: 1 | 158 |

|-----------------------------|-----|

| MAX9141 TRANSISTOR COUNT: 1 | 92  |

| MAX9142 TRANSISTOR COUNT: 3 | 314 |

| MAX9144 TRANSISTOR COUNT: 6 | 620 |

| PROCESS: Bipolar            |     |

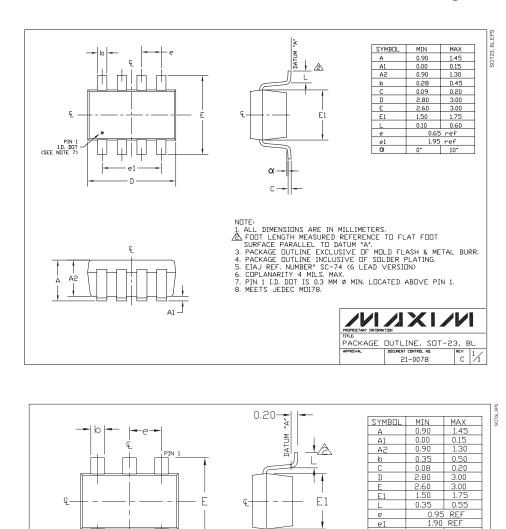

e1

D Ģ

Α1

NUIES: 1. ALL DIMENSIONS ARE IN MILLIMETERS. A FOOT LENGTH MEASURED AT INTERCEPT POINT BETWEEN DATUM A & LEAD SURFACE. 3. PACKAGE OUTLINE EXCLUSIVE OF MOLD FLASH & METAL BURR. 4. PACKAGE OUTLINE INCLUSIVE OF SOLDER PLATING.

Α2 Α ŧ

NDTES:

5. MEETS JEDEC MO178.

#### Package Information

α~

LI-C

۵

21-0057

SL REV 1

PACKAGE DUTLINE, SDT-23,

///XI//

#### Package Information (continued)

MAX9140/MAX9141/MAX9142/MAX9144

ΕН Ħ F F F 0°-8° INCHES MILLIMETERS INCHES MILLIMETERS MIN MAX MIN MAX MIN МАХ MIN MAX N MS012 0.069 1.35 1.75 0.189 0.197 5.00 8 0.053 4.80 А D А 8.55 0.10 0.25 D 0.337 0.344 8.75 14 A1 0.004 0.010 В D 0.386 B 0.014 0.019 0.35 0.49 0.394 9.80 10.00 16 С 0.007 0.010 0.19 0.25 С 0.050 1.27 e NDTES: 3.80 4.00 D&E DO NOT INCLUDE MOLD FLASH F 0.150 0.157 1. 2. MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .15mm (.006') 3. LEADS TO BE COPLANAR WITHIN .102mm (.004') H 0.228 0.244 5.80 6.20 0.010 0.020 0.25 0.50 h 0.050 0.40 1.27 L 0.016 . DOCHNICUUY / CUNTROLLING DIMENSION: MILLIMETER 5. MEETS JEDEC MS012-XX AS SHOWN IN ABOVE TABLE 6. N = NUMBER OF PINS PACKAGE FAMILY DUTLINE: SDIC .150" 21-0041 A unent control n

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

12

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 2001 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.

Package Information (continued)

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.