# Si85xx Unidirectional AC Current Sensors

#### **Features**

- Single-chip ac current sensor

- Low loss: <1.3 mΩ primary series resistance and <2 nH inductance

- Leading-edge noise suppression eliminates need for leading-edge blanking

- "Ping-Pong" output version allows one Si85xx to replace two current transformers in full-bridge designs

- 5, 10, and 20 A full-scale versions

- ±5% initial accuracy

- 50 kHz to 1 MHz input frequency range

- FAULT output to safeguard operation

- Large 2 V<sub>PP</sub> min output at full scale

- High-side or low-side current sensing

- Compact 4x4x1 mm QFN package (1 kV<sub>RMS</sub> isolation)

- 20-pin wide-body SOIC (5 kV<sub>RMS</sub> isolation)

- -40 to 125 °C operating range

- UL/VDE/CSA approval

### **Applications**

- Power supplies

- Motor controls

- Lighting equipment

- Industrial equipment

### **Description**

The Si85xx products are unidirectional ac current sensors available in full-scale ranges of 5, 10, and 20 A. Si85xx products are ideal upgrades for older current-sensing technologies offering size, performance, and cost advantages over current transformers, Hall effect devices, DCR circuits, and other approaches. The Si85xx are extremely low-loss, adding less than 1.3 m $\Omega$  of series resistance and less than 2 nH series inductance in the sensing path at 25 °C. Current-sensing terminals are isolated from the other package pins, providing up to 5 kV<sub>RMS</sub> isolation level per safety approval ratings.

#### Safety Approval (20-Pin SOIC Only)

- UL 1577 recognized

- 5000 V<sub>RMS</sub> for 1 minute

- CSA component notice 5A approval

- IEC 60950, 61010, 60601 approved

- VDE certification conformity\*

- IEC 60747-5-2 (VDE0884 Part 2)

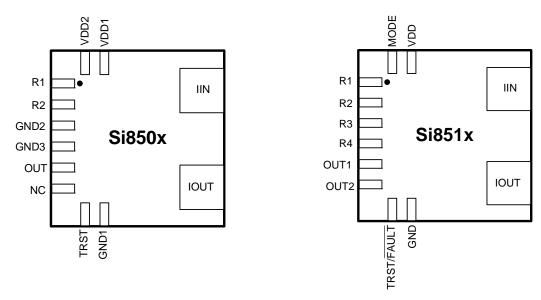

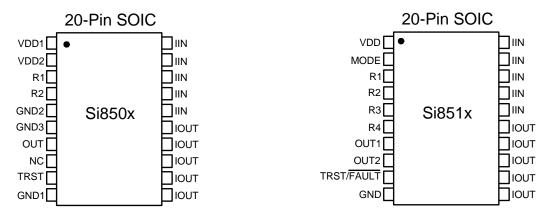

#### Pin Assignments: See page 24 20-Pin SOIC VDD[ MODE Піім R1 IIIN R2 IIN R3 Si851x IIN IOUT R4 OUT1 IOUT IOUT OUT2 TRST/FAULT IOUT TIOUT GND 12-Pin QFN IIN R2 R3 Si851x R4 OUT1 TUOI GND rrst/<u>fault</u>

Patents pending

### **Functional Block Diagram**

\*Note: Pending

# TABLE OF CONTENTS

| <u>Section</u> <u>F</u>                           | Page |

|---------------------------------------------------|------|

| 1. Electrical Specifications                      | 4    |

| 2. Functional Overview                            | 9    |

| 2.1. Under Voltage Lockout (UVLO)                 | 10   |

| 2.2. Device Startup                               |      |

| 2.3. Integrator Reset and Current Measurement     |      |

| 2.4. Total Measurement Error                      |      |

| 2.5. Effect of Temperature on Accuracy            |      |

| 2.6. Leading Edge Noise Suppression               |      |

| 2.7. FAULT Output                                 |      |

| 2.8. Safe Operating Limits                        |      |

| 3. Application Information                        | 13   |

| 3.1. Board Layout                                 | 13   |

| 3.2. SOIC Layout Requirements                     | 13   |

| 3.3. Device Configuration                         | 14   |

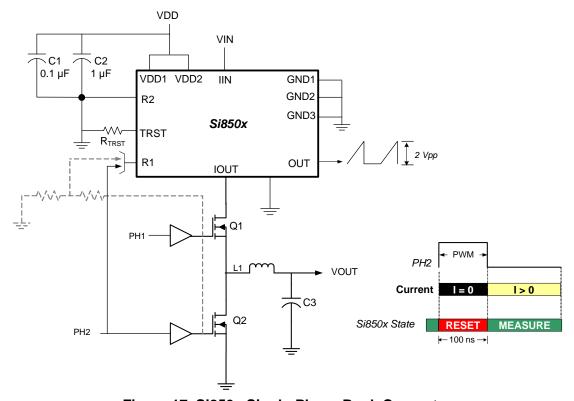

| 3.4. Single-Phase Buck Converter Example          | 21   |

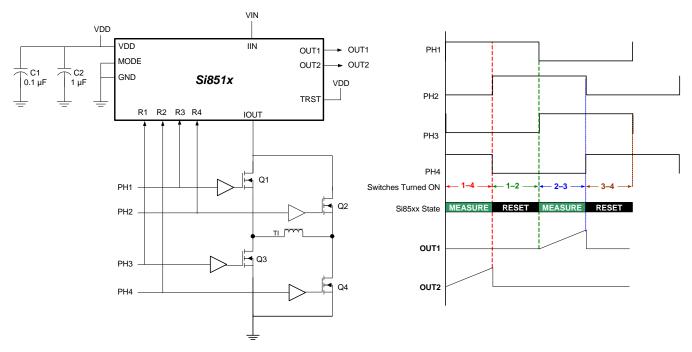

| 3.5. Full-Bridge Converter Example                |      |

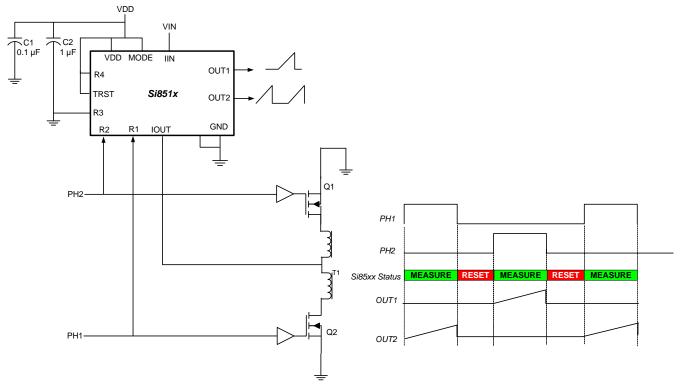

| 3.6. Push-Pull Converter Example                  | 23   |

| 4. Pin Descriptions—12-Pin QFN                    | 24   |

| 5. Pin Descriptions—20-Pin SOIC                   | 25   |

| 6. Ordering Guide                                 |      |

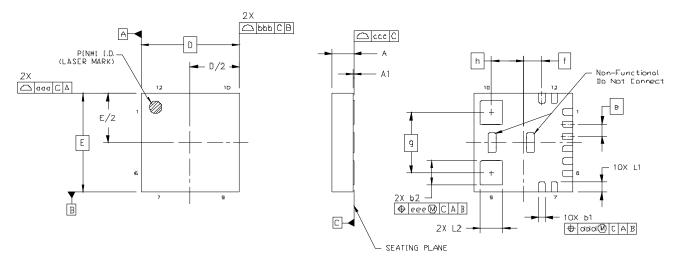

| 7. Package Outline—12-Pin QFN                     | 27   |

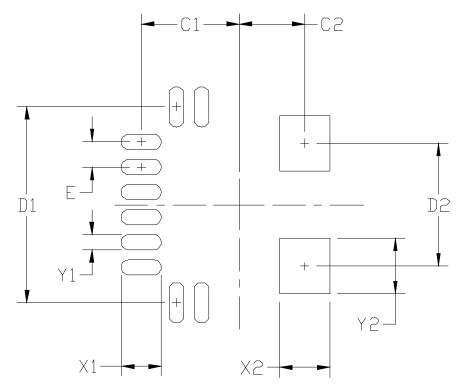

| 8. Recommended PCB Landing Pattern (12-Pin QFN)   | 28   |

| 9. Top Marking (QFN)                              |      |

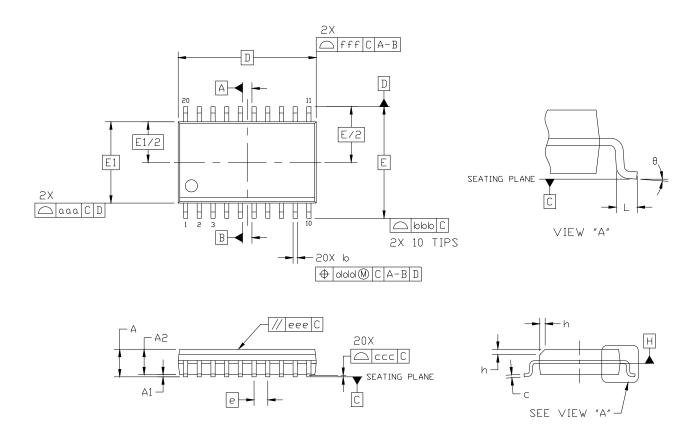

| 10. Package Outline: Wide Body SOIC               | 30   |

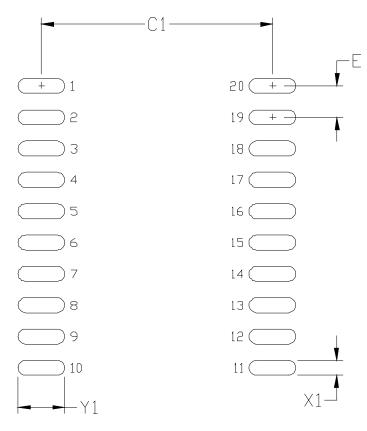

| 11. Recommended PCB Landing Pattern (20-Pin SOIC) | 32   |

| 12. Top Marking (SOIC)                            |      |

| Document Change List                              | 34   |

| Contact Information                               | 36   |

# 1. Electrical Specifications

**Table 1. Electrical Specifications**

$T_A = -40$  to +125 °C (typical specified at 25 °C), VDD = 3 V (±10%) to 5 V (±10%), f = 400 kHz, unless specified

| Parameter                                                | Conditions                                                            | Min  | Тур | Max  | Unit      |

|----------------------------------------------------------|-----------------------------------------------------------------------|------|-----|------|-----------|

| Supply Voltage (V <sub>DD</sub> )                        |                                                                       | 2.7  | _   | 5.5  | V         |

| Supply Current Fully enabled, input frequency = 1 MHz    |                                                                       | _    | 4   | 7    | mA        |

| Undervoltage Lockout (V <sub>UVLO</sub> )                |                                                                       | 2.1  | 2.3 | 2.5  | V         |

| Undervoltage Lockout Hysteresis<br>(V <sub>HYST</sub> )  |                                                                       | _    | 100 | _    | mV        |

| Logic Input HIGH Level                                   | MODE, R1, R2, R3, R4 inputs                                           | 2.0  | _   | _    | V         |

| Logic Input LOW Level                                    | (TTL compatible)                                                      | _    | _   | 8.0  | V         |

| Reset Time (t <sub>R</sub> )                             | Time for 5% initial accuracy                                          | 150  | _   | _    | ns        |

| Reset Time Resistor Range <sup>1</sup>                   |                                                                       | 15   | _   | 2500 | kΩ        |

| R1, R2, R3, R4 Input Rise Time (t <sub>RR</sub> )        |                                                                       | _    | _   | 30   | ns        |

| R1, R2, R3, R4 Input Fall Time (t <sub>FR</sub> )        |                                                                       | _    | _   | 30   | ns        |

| Measurement Watchdog Timeout (t <sub>WD</sub> )          |                                                                       | 30   | 50  | 80   | μs        |

| Series Input Resistance                                  | Measured from IIN to IOUT                                             | _    | 1.3 | _    | mΩ        |

| Series Inductance                                        | Measured from IIN to IOUT                                             | _    | 2   | _    | nΗ        |

| Input/Output Delay <sup>1</sup>                          | OUT, OUT1, OUT2 delay relative to input                               | _    | 150 | 200  | ns        |

| Start-Up Self-Cal Delay (t <sub>CAL</sub> ) <sup>1</sup> | Time from VDD = V <sub>UVLO</sub> + V <sub>HYST</sub> to cal complete | _    | 150 | 200  | μs        |

| Input Common Mode Voltage Range                          | 4x4 mm QFN                                                            | 1000 | _   | _    | $V_{RMS}$ |

| (dc) <sup>1</sup>                                        | SOIC-20                                                               | 5000 | _   | _    | $V_{RMS}$ |

| Operating Input Frequency Range (f) <sup>1</sup>         |                                                                       | 50   | _   | 1000 | kHz       |

| DC Power Supply Rejection Ratio                          |                                                                       | _    | 40  | _    | db        |

| Sensitivity @ VDD = 3 V                                  | Si8501/11/17                                                          | _    | 404 | _    | mV/A      |

|                                                          | Si8502/12/18                                                          | _    | 202 | _    | mV/A      |

|                                                          | Si8503/13/19                                                          | _    | 101 | _    | mV/A      |

| Sensitivity @ VDD = 5 V                                  | Si8501/11/17                                                          | _    | 392 | _    | mV/A      |

|                                                          | Si8502/12/18                                                          | _    | 196 | _    | mV/A      |

|                                                          | Si8503/13/19                                                          |      | 98  |      | mV/A      |

| Matan                                                    |                                                                       |      |     |      |           |

- **1.** Guaranteed by design and/or characterization.

- 2. Maximum output load is not recommended to exceed 200 pF and 5 k $\Omega$ .

- 3. Production tested at 400 kHz (50% duty cycle) at VDD = 3.3 V.

- **4.** See "2.4. Total Measurement Error" on page 11 for more information.

### **Table 1. Electrical Specifications (Continued)**

$T_A = -40$  to +125 °C (typical specified at 25 °C), VDD = 3 V (±10%) to 5 V (±10%), f = 400 kHz, unless specified

| Parameter                                                | Conditions                                                | Min | Тур | Max | Unit |

|----------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| OUT, OUT1, OUT2 Offset Voltage<br>(V <sub>OUTMIN</sub> ) | Current flow from I <sub>IN</sub> to I <sub>OUT</sub> = 0 | _   | 50  |     | mV   |

| V <sub>OUT</sub> Slew Rate <sup>1,2</sup>                | OUT, OUT1, OUT2 load = 5K    50 pF                        | _   | 50  | 1   | V/µs |

| OUT, OUT1, OUT2 Output Resistance                        |                                                           | 20  | _   | 130 | Ω    |

| Total Measurement Error (%)                              | 20% of full scale <sup>3,4</sup> (all devices)            | -30 | _   | +30 | %    |

| (–40 to 125 °C Temp Range)                               | 100% of full scale <sup>3,4</sup>                         | -10 | _   | +10 | %    |

#### Notes:

- **1.** Guaranteed by design and/or characterization.

- 2. Maximum output load is not recommended to exceed 200 pF and 5 k $\Omega$ .

- 3. Production tested at 400 kHz (50% duty cycle) at VDD = 3.3 V.

- 4. See "2.4. Total Measurement Error" on page 11 for more information.

# Table 2. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                                           | Symbol               | Min   | Тур | Max       | Units     |

|---------------------------------------------------------------------|----------------------|-------|-----|-----------|-----------|

| Storage temperature                                                 | T <sub>STG</sub>     | -65   |     | +150      | °C        |

| Ambient temperature under bias                                      | T <sub>A</sub>       | -40   |     | +125      | °C        |

| Supply voltage                                                      | V <sub>DD</sub>      | _     | _   | 5.75      | V         |

| Voltage on any pin with respect to ground (not including IIN, IOUT) | V <sub>IN</sub>      | -0.5  | _   | VDD + 0.5 | V         |

| Output Current Drive                                                | L <sub>O</sub>       | _     |     | 10        | mA        |

| Lead solder temperature (10 s)                                      |                      | _     |     | 260       | ٥C        |

| Maximum Input Current Rate of Change                                |                      | _     |     | 1000      | A/µs      |

| Maximum Peak AC Input Current Limit                                 |                      | _     |     | 200       | Α         |

| Thermal Limit (DC Current) <sup>2</sup>                             |                      | _     | _   | 30        | Α         |

| Maximum Isolation Voltage (QFN)                                     |                      | _     | _   | 1400      | $V_{RMS}$ |

| Maximum Isolation Voltage (SOIC-20)                                 |                      | _     |     | 6000      | $V_{RMS}$ |

| ESD (CDM)                                                           | JEDEC (JESD22-C101C) | -1.5  |     | +1.5      | kV        |

| ESD (HBM)                                                           | JEDEC (JESD22-A114E) | -2500 |     | +2500     | V         |

| ESD (MM)                                                            | JEDEC (JESD22-A115A) | -250  |     | + 250     | V         |

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Refer to "AN329: Extending the Full-Scale Range of the Si85xx" for more information.

### Table 3. Regulatory Information<sup>1</sup> (SOIC-20 Only)

#### **CSA**

The Si85xx is certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

#### $\mathsf{VDE}^2$

The Si85xx is certified according to IEC 60747-5-2. For more details, see File 5006301-4880-0001.

#### UL

The Si85xx is certified under UL1577 component recognition program. For more details, see File E257455.

#### Notes

- All 5.0 kV<sub>RMS</sub> rated devices are production tested to ≥4.8 kV<sub>RMS</sub> for 1 sec. For more information, see "6. Ordering Guide" on page 26.

- 2. Pending.

#### **Table 4. Insulation and Safety-Related Specifications**

| Parameter                                        | Symbol          | Test Condition                | Value            | Unit |

|--------------------------------------------------|-----------------|-------------------------------|------------------|------|

|                                                  |                 |                               | SOIC-20          |      |

| Minimum Air Gap (Clearance)                      | L(101)          |                               | 7.6 min          | mm   |

| Minimum External Tracking (Creepage)             | L(102)          |                               | 7.6 min          | mm   |

| Minimum Internal Gap<br>(Internal Clearance)     |                 |                               | 0.2              | mm   |

| Tracking Resistance (Comparative Tracking Index) | CTI             | DIN IEC 60112/VDE 0303 Part 1 | >175             | V    |

| Resistance (Input-Output) <sup>1</sup>           | R <sub>IO</sub> |                               | 10 <sup>12</sup> | Ω    |

| Capacitance (Input-Output) <sup>1</sup>          | C <sub>IO</sub> | f = 1 MHz                     | 1.4              | pF   |

| Input Capacitance <sup>2</sup>                   | C <sub>I</sub>  |                               | 4.0              | pF   |

#### Notes:

- 1. To determine resistance and capacitance, the Si85xx is converted into a 2-terminal device. Pins 1–10 are shorted together to form the first terminal and pins 11–20 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

- 2. Measured from input pin to ground.

#### Table 5. IEC 60664-1 (VDE 0884 Part 2) Ratings

| Parameter                   | Test Conditions                              | Specification |

|-----------------------------|----------------------------------------------|---------------|

|                             |                                              | SOIC-20       |

| Basic Isolation Group       | Material Group                               | Illa          |

|                             | Rated Mains Voltages ≤ 150 V <sub>RMS</sub>  | I-IV          |

|                             | Rated Mains Voltages ≤ 300 V <sub>RMS</sub>  | I-IV          |

| Installation Classification | Rated Mains Voltages ≤ 400 V <sub>RMS</sub>  | I-IV          |

|                             | Rated Mains Voltages ≤ 600 V <sub>RMS</sub>  | I-IV          |

|                             | Rated Mains Voltages ≤ 1000 V <sub>RMS</sub> | 1-111         |

Table 6. IEC 60747-5-2 Insulation Characteristics\*

| Parameter                                                                       | Symbol            | Test Condition                                                                                                                                       | Characteristic   | Unit   |

|---------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|

|                                                                                 |                   |                                                                                                                                                      | SOIC-20          |        |

| Maximum Working Insulation Voltage                                              | V <sub>IORM</sub> |                                                                                                                                                      | 1414             | V peak |

|                                                                                 |                   | Method a After Environmental Tests Subgroup 1 (V <sub>IORM</sub> x 1.6 = V <sub>PR</sub> , t <sub>m</sub> = 60 sec, Partial Discharge < 5 pC)        | 2262             |        |

| Input to Output Test Voltage                                                    | V <sub>PR</sub>   | Method b1<br>(V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100%<br>Production Test, t <sub>m</sub> = 1 sec,<br>Partial Discharge < 5 pC)            | 2652             | V peak |

|                                                                                 |                   | After Input and/or Safety Test<br>Subgroup 2/3<br>(V <sub>IORM</sub> x 1.2 = V <sub>PR</sub> , t <sub>m</sub> = 60 sec,<br>Partial Discharge < 5 pC) | 1697             |        |

| Highest Allowable Overvoltage (Transient Overvoltage, t <sub>TR</sub> = 10 sec) | V <sub>TR</sub>   |                                                                                                                                                      | 8000             | V peak |

| Pollution Degree (DIN VDE 0110, Table 1)                                        |                   |                                                                                                                                                      | 2                |        |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V               | R <sub>S</sub>    |                                                                                                                                                      | >10 <sup>9</sup> | Ω      |

\*Note: The Si85xx is suitable for basic and reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The Si85xx provides a climate classification of 40/125/21. Note that the Si85xx is compliant with the IEC60747-5-2 but neither certified nor inspected to IEC60747-5-2. The Si85xx is compliant, certified, and factory-inspected to IEC60950.

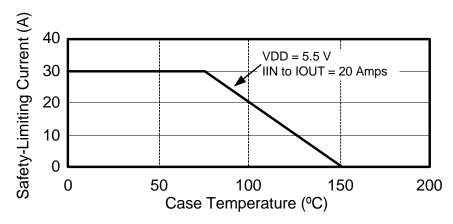

### Table 7. IEC Safety Limiting Values<sup>1</sup>

| Parameter                             | Symbol         | Test Condition                                                                                                      | SOIC-20 | Unit |

|---------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|---------|------|

| Case Temperature                      | T <sub>S</sub> |                                                                                                                     | 150     | °C   |

| Safety Input Current                  | I <sub>S</sub> | $\theta_{JA} = 85, V_{DD} = 5.5 V,$ IIN to IOUT = 20 A, $T_{J} = 150 ^{\circ}\text{C}, T_{A} = 25 ^{\circ}\text{C}$ | 30      | A    |

| Device Power Dissipation <sup>2</sup> | P <sub>D</sub> |                                                                                                                     | 0.9     | W    |

- 1. Maximum value allowed in the event of a failure. Refer to the thermal derating curve in Figure 1.

- 2. The Si85xx is tested with  $V_{DD}$  = 5.5 V,  $T_J$  = 150 °C,  $C_L$  = 15 pF, and with an input current from IIN to IOUT equal to 20 Amps at 500 kHz (duty cycle = 50%).

**Table 8. Thermal Characteristics**

| Parameter                             | Symbol            | Test Condition | SOIC-20 | 4x4 mm<br>QFN | Unit |

|---------------------------------------|-------------------|----------------|---------|---------------|------|

| IC Junction-to-Air Thermal Resistance | $\theta_{\sf JA}$ |                | 85      | 55            | °C/W |

Figure 1. SOIC-20 Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN EN 60747-5-2

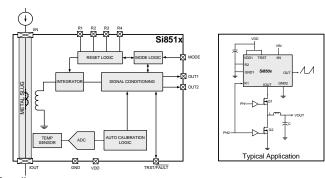

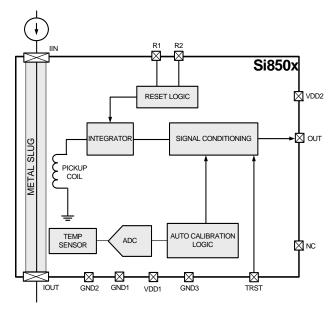

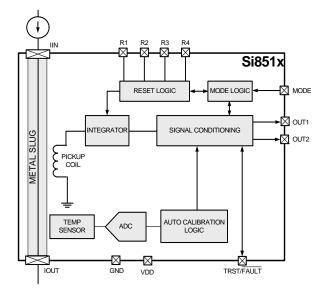

#### 2. Functional Overview

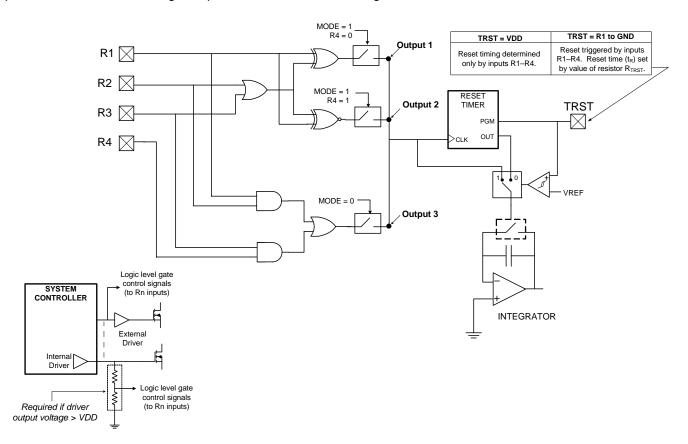

The Si85xx ac current sensor family of products mimics the functionality of traditional current transformer (CT) circuits with burden resistor, diode, and output filter, but offers enhanced performance and added capabilities. These devices use inductive current sensing and onboard signal conditioning electronics to generate a 2 V full-scale output signal proportional to the ac current flowing from the IIN to the IOUT terminals. As shown in Figures 2 and 3, current flowing through the metal package slug induces a signal in the pickup coil on the Si85xx die. This signal is applied to the input of an integrator that reconstructs the ac current flowing from IIN to IOUT. Onboard circuitry provides cycle-by-cycle integrator reset and temperature and offset voltage compensation to achieve initial measurement accuracy to within ±5%.

Figure 2. Si850x (Single Output) Block Diagram

Figure 3. Si851x (Ping Pong Output) Block Diagram

The Si85xx is superior to other current sensing approaches and benefits the system in a number of ways:

- **Small size:** With its 4x4 mm footprint and 1 mm height (QFN package option), the Si85xx is among the smallest current sensors available.

- Large output signal: The nominal 2.0 V full-scale output swing offers superior noise immunity versus other current sensing technologies.

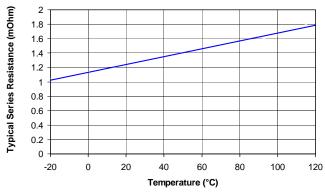

- Low loss: The Si85xx adds only 1.3 mΩ (at 25 °C) to the sensing path, making it one of the lowest-loss current sensors available. Low 2 nH primary series inductance is 2,000 times lower compared to a CT and results in significantly less ringing.

- High precision: All versions are available with an initial maximum error of ±5% of reading; one of the most accurate current sensors available.

- Ping-Pong output mode (Si851x): Alternately routes the current measurements from each side of a full-bridge circuit to separate output pins for comparison, which is very useful for transformer flux balancing applications. Eliminates a second CT in a full-bridge application.

- Leading edge noise suppression: Filters out reflected noise due to long reverse recovery time of output rectifier. Eliminates the need for external leading edge blanking circuit.

- High common-mode voltage: The Si85xx offers a minimum of 1,000 V<sub>RMS</sub> (for QFN package) or 5 kV<sub>RMS</sub> (for SOIC package) of common-mode voltage range (or isolation), making it useful over a very wide voltage range.

- FAULT output (Si8517/8/9): Goes low when external reset timing is in error.

- Ease-of-use: Other than conventional power and grounding techniques, no special board layout considerations are required. Built-in timing interface circuits allow already-available system switching signals to be used for reset with no external circuits required.

#### 2.1. Under Voltage Lockout (UVLO)

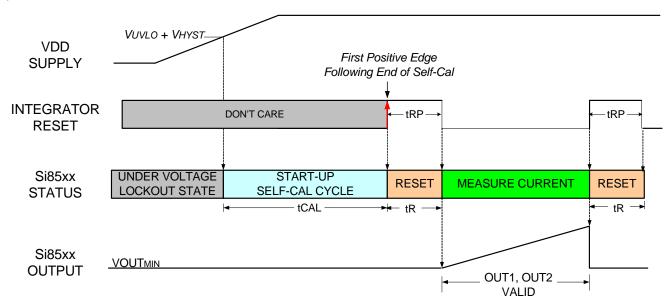

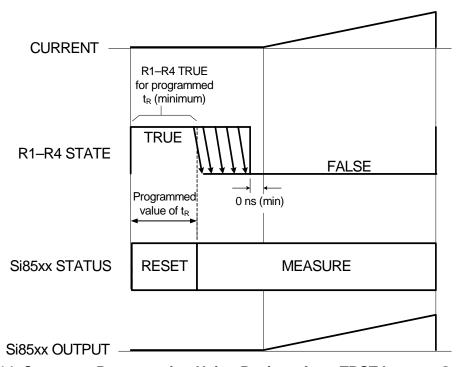

UVLO is provided to prevent erroneous operation during device start-up and shutdown or when VDD is significantly below the specified operating range. The Si85xx is in UVLO state when VDD  $\leq$  VUVLO (Figure 4). During UVLO, the output(s) are held at minimum value regardless of the amount of current flowing from IIN to IOUT, and signals on integrator reset inputs R1–R4 are ignored. The Si85xx exits UVLO when VDD  $\geq$  (VUVLO + VHYST).

### 2.2. Device Startup

Upon exit from UVLO, the Si85xx performs a voltage offset and temperature self-calibration cycle. During this time, output(s) are held at minimum value and reset inputs (R1-R4) are ignored. The reset inputs are enabled at the end of the self-calibration cycle, and an integrator reset cycle is initiated on the first occurrence of active signals on R1-R4. A current measurement is initiated immediately after the completion of the integrator reset cycle, and the resulting current waveforms appear on the output pins. This "reset-measure-reset" pattern repeats throughout steady-state operation.

# 2.3. Integrator Reset and Current Measurement

The Si85xx measures current flowing from the IIN to IOUT terminals. Current is allowed to flow in the opposite direction, but will not be measured (OUT1 and OUT 2 remain at their minimum values during reverse current flow. Reverse current flow will not damage the Si85xx).

To achieve the specified accuracy, the integrator capacitor must be discharged (reset) for time period  $t_R$  prior to the start of every measurement cycle. This cycle-by-cycle reset is implemented by connecting existing system gate control signals to the R1–R4 inputs in a way that resets the integrator when no current is flowing from IIN to IOUT. To achieve rated accuracy, the reset cycle must be completed prior to the start of the measurement cycle. For maximum flexibility, integrator reset operation can be configured in one of two ways:

Option 1: The start and duration of reset is determined by the states of the timing signals applied to R1–R4.

Option 2: The timing signals applied to R1–R4 trigger the start of reset, and the duration of the reset is determined by an onboard programmable reset timer.

Figure 4. Si85xx Startup and Control Timing

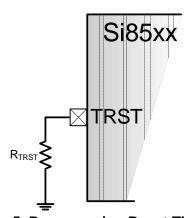

Integrator reset Option 1 is selected by connecting  $T_{RST}$  to VDD. In this mode, the Si85xx is held in reset as long as the signals on R1–R4 satisfy the logic equations of Table 11. It is typically used in applications where the gate drivers are external to the system controller IC (the gate driver delay ensures reset is completed prior to the start of measurement).

Reset Option 2 is selected by connecting a timing resistor (R<sub>TRST</sub> in Figure 5) from the TRST input to ground. It is typically used in applications where the gate drivers are on-board the controller. In this mode, the on-chip reset timer is triggered when the signals on R1-R4 satisfy the logic equations in Table 11. Once triggered, the timer maintains integrator in reset for time duration t<sub>R</sub> as programmed by the value of resistor R<sub>TRST</sub>. The user must select the value of resistor R<sub>TRST</sub>. to terminate the reset cycle prior to the start of measurement under worst-case timing conditions. Note that values of t<sub>R</sub> below the specified value in "1. Electrical Specifications" on page 4 results in increased integrator output offset error and increased output noise on VOLIT. Moreover, tR's time is summarized by the following equation (see Table 9):

$$t_R = 10 \text{ ns/k}\Omega$$

where values of R<sub>TRST</sub> that produce a reset time less than 150 ns (R<sub>TRST</sub>  $\leq$  15 k $\Omega$ ) should not be used.

Figure 5. Programming Reset Time (t<sub>R</sub>)

Table 9. Typical Reset Time vs. R<sub>TRST</sub> Resistance

| R <sub>TRST</sub> | Reset Time (t <sub>R</sub> ) |

|-------------------|------------------------------|

| 15 kΩ             | 150 ns                       |

| 100 kΩ            | 1 µs                         |

| 1 ΜΩ              | 9 µs                         |

| 2.2 ΜΩ            | 2 µs                         |

#### 2.4. Total Measurement Error

The Si85xx's absolute accuracy is affected by the following factors:

- Ambient operating temperature

- VDD supply voltage

- Time

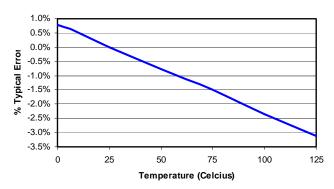

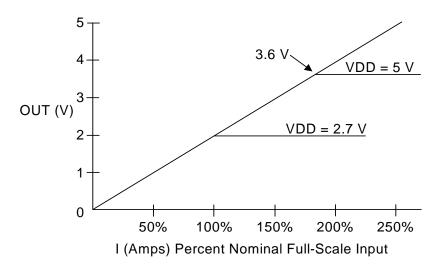

Table 10 includes a composite of all environmental and operating conditions that can ultimately affect the absolute measurement accuracy of the Si85xx. The total worst-case accuracy at full scale can be estimated by the sum of the initial accuracy (up to  $\pm 5\%$ ) plus aging (up to  $\pm 1.5\%$ ) and supply variations (up to  $\pm 3.5\%$ ). For example, the total measurement error expected for a device operating at a given V<sub>DD</sub> supply of 5 V ( $\pm 10\%$ ) is 10% if the device is operated over a temperature range of -40 to 125 °C for up to 10 years. If the temperature range is limited to 0 to 85 °C, the measurement error can be improved by up to 2%. See Figure 6 for details.

Table 10. Total Measurement Error Contributors

| Error Contributor                                    | % Error Added |

|------------------------------------------------------|---------------|

| Initial error<br>@ given V <sub>DD</sub> ±10%, 25 °C | ±5%           |

| Temperature variation<br>–40 to 125 °C               | ±3.5%         |

| Aging (10 years)                                     | ±1.5%         |

### 2.5. Effect of Temperature on Accuracy

Offset voltage present at the Si85xx output terminals (output offset voltage) is calibrated out each time VDD is applied to the Si85xx; so, its error contribution is minimized when the temperature at which calibration occurred is at or near the steady-state operating temperature of the Si85xx. For example, applying VDD at 25 °C (offset cal is performed) and operating at 85 °C will result in a larger offset error than operating at 50 °C. The effect of this error is summarized in Figure 6. The chart is referenced to 25 °C. If the Si85xx is powered up at 25 °C and then operated at 125 °C with no autocalibration performed (i.e., the power is not cycled at 125 °C, which causes an auto-calibration), a 3% measurement error can be expected.

Figure 6. Differential Temperature

Calibration Error

Figure 7 shows the Si85xx thermal characteristics of the on-chip sense resistance over the temperature range of –40 to +125 °C. Series inductance is constant at 2 nH (max) across this same temperature range.

Figure 7. Series Resistance Thermal Characteristics

#### 2.6. Leading Edge Noise Suppression

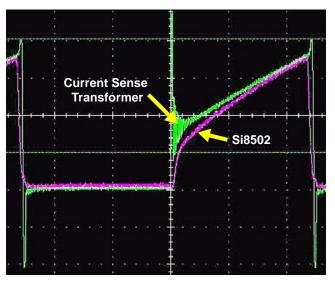

High-amplitude spikes on the leading edge of the primary switching waveforms can cause the PWM latch to be erroneously reset at the start of the switching cycle when operating in current mode control. To prevent this problem, leading edge blanking is commonly used to disable the current comparator during the early portion of the primary-side switching cycle. The Si85xx eliminates leading-edge noise spikes by including them in the signal integration. As shown in the output waveform of Figure 8 (Si8502 waveform measured directly on OUT pin with no external filter), noise present in the input waveform is eliminated without the use of blanking.

Figure 8. Leading-Edge Noise Suppression Waveforms (200 kHz, 9.3 A Load)

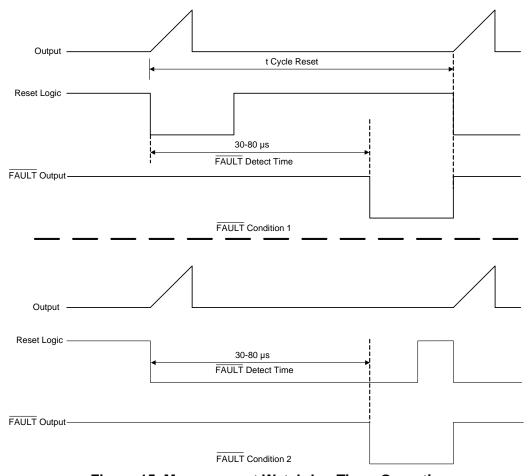

# 2.7. FAULT Output

The  $\overline{\text{FAULT}}$  output (Si8517/8/9) guards against Si85xx output signal errors caused by missing reset cycles. FAULT is asserted when a measurement cycle exceeds the internal watchdog timer times limit of  $t_{WD}$ . FAULT can be used to alert a local microcontroller or digital power controller of a current sense failure or to initiate a system shutdown. To detect faults, tie a 200 k $\Omega$  resistor from TRST/FAULT to VDD.

#### 2.8. Safe Operating Limits

The Si85xx is a very robust current sensor. Its maximum input current rate of change is limited to 1000 A/µs. The maximum peak ac input current limit is 200 A. The thermal limit or continuous dc current flow limit is 30 A. Exceeding these limits may cause long-term reliability issues. Refer to "AN329: Extending the Full-Scale Range of the Si85xx" for more information.

### 3. Application Information

### 3.1. Board Layout

The Si85xx is connected in the series path of the current to be measured. The Si85xx must be located as far as possible from transformer and other magnetic field sources. Like other analog components, the Si85xx should be powered from a low-noise dc source and, preferably, to a low-noise analog ground plane. Recommended bypass capacitors are 1  $\mu$ F in parallel with a 0.1  $\mu$ F, positioned as close to the Si85xx as possible. When using the Si850x (single output versions), all 3 ground pins MUST be connected to the same ground point, and both VDD and VDD2 pins MUST be tied to VDD.

### 3.2. SOIC Layout Requirements

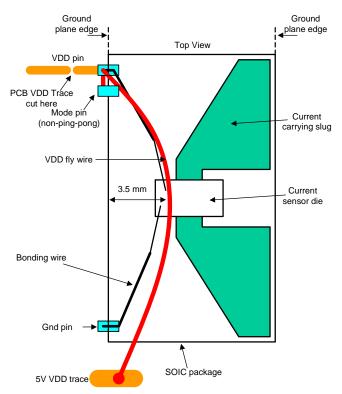

The Si85xx SOIC package version requires special layout techniques to ensure proper operation. Due to the large SOIC package seize and close proximity of the current-carrying slug and current sensor silicon, magnetic coupling between the current-carrying slug and the silicon can form a ground loop causing the output voltage to be 0 V even though current is flowing through the slug. To eliminate any such coupling issues, a red fly-wire VDD trace as shown in Figure 9 should be implemented in the layout for the SOIC package. The red fly-wire trace should be approximately 3.5 mm from the center edge of the package intersecting approximately in the center of the package. Standard wire thicknesses for 10 mA current-carrying capabilities should be used. Note also that any ground planes should be moved to the edge of the package.

Figure 9. SOIC Layout Requirements

Regarding isolation voltage requirements, the trace does not need to follow the lead frame and bonding traces exactly, as long as the net magnetic flux is close to zero. The goal here is to keep the magnetic coupling small and, at the same time, keep the isolation distance large. Moreover, to ensure that the layout meets the and design's required creepage clearance requirements, the VDD trace should be placed on one of the inner layers or even the back side of the board. For example, one can lay out the return VDD trace on the other side of the PCB so the PCB itself can help to provide high isolation voltage.

### 3.3. Device Configuration

Configuring the Si85xx involves the following steps:

- 1. Selecting an output mode

- 2. Configuring integrator reset timing

- 3. Setting integrator reset time t<sub>R</sub>

#### 3.3.1. Device Selection

The Si85xx family offers three output modes: Single output (Si850x), and 2 and 4-Wire Ping Pong (Si851x). The Si851x products can be configured to operate in all three of these output modes.

The Si850x products operate ONLY in Single output mode. Most half-wave and single-phase applications require only Single output mode and will typically use the Si850x.

In Single output mode, output current always appears on the OUT pin (Si850x) or the OUT1 pin (Si851x). A single integrator reset signal is typically sufficient when operating in this mode.

Ping-Pong mode routes the current waveform to two different output pins on alternate measurement cycles. It is useful in full-wave and push-pull topologies where external circuitry can be used to monitor and/or control transformer flux balance. (Section "3. Application Information" on page 13 shows design examples using both output modes in various power topologies.)

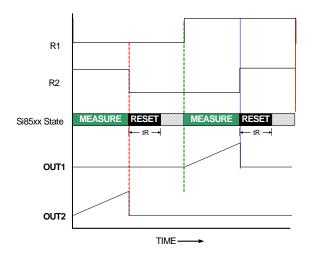

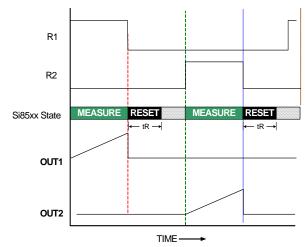

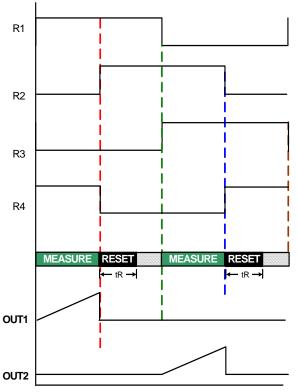

2-wire Ping-Pong mode is useful mainly in non-overlapping two-phase buck converters but may also be used in full-bridge applications. In this output mode, reset inputs R1 and R2 are used, and input R3 is grounded. Measured current appears on OUT1 when R1 is high and on OUT2 when R2 is high as shown in the full-bridge timing example of Figures 10 and 11.

Figure 10. Two-Phase Buck Timing Example A

Figure 11. Full-Bridge Timing Example B

4-Wire Ping-Pong mode is recommended for full-bridge applications over 2-wire because it uses all four inputs, making the reset function tolerant to single-point signal failures. In 4-Wire Ping-Pong mode, current appears on OUT2 when R1 is high and R2 is low, and appears on OUT1 when R3 is high and R4 is low as shown in the full-bridge timing example of Figure 12. Table 11 shows the states of the Mode and R4 inputs that select each output, and the resulting reset logic functions and truth tables.

Figure 12. Full-Bridge Timing Example C

#### 3.3.2. Selecting Reset Timing Signals

Reset timing signals should be chosen to meet the following conditions:

- Satisfy reset time t<sub>R</sub>

- Not overlap integrator reset into the desired measurement period

- Not violate reset watchdog timeout period t<sub>WD</sub>

#### 3.3.3. Configuring Integrator Reset

Per Section "2. Functional Overview", the integrator must be reset (zeroed) prior to the start of each measurement cycle to achieve specified measurement accuracy. This reset must be synchronized with the system switch timing signals to ensure that current is measured during the appropriate time; so, the Si85xx integrator reset circuitry uses system timing as its reference. Timing signals connect to reset inputs R1 through R4 where built-in logic functions allow the user to choose the conditions that cause an integrator reset event. Important Note: reset inputs R1–R4 are rated to a maximum input voltage of VDD. External resistor dividers must be used when connecting driver output signals to R1–R4 that swing beyond VDD.

As shown in Table 11, the Si850x integrator reset logic is a simple XOR gate where reset is maintained (or triggered, depending on use of the TRST input) when states of reset inputs R1 and R2 are not equal.

Figure 13 shows the logic for the Si851x products, where any one of three reset logic functions can cause integrator reset. The output mode (Si851x) is determined by the states of the Mode and R4 inputs, as shown in Table 11.

Table 11. Si85xx Output and Reset Mode Summary

| Output Mode        | MODE | R4 | R3 | R2 | R1 | Reset<br>State* | Reset Logic Expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------|----|----|----|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |      |    |    | 0  | 0  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    | 0  | 0  | 1  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    | 0  | 1  | 0  | 1               | RESET = XOR[R1, (R2 R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Single-Ended       | 1    | 0  |    | 1  | 1  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Single-Linded      | Į.   | U  |    | 0  | 0  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    | 1  | 0  | 1  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    | '  | 1  | 0  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    |    | 1  | 1  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2-Wire Ping Pong   |      |    |    | 0  | 0  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | 1    | 1  | 0  | 0  | 1  | 0               | RESET = XNOR[R1,(R2 R3)]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | '    | '  |    | 1  | 0  | 0               | (\text{\text{Col}   - \text{\text{NON[(\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\ticl{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tint{\text{\text{\text{\text{\text{\text{\text{\ticl{\text{\tint{\text{\tint{\text{\tint{\tint{\text{\text{\text{\text{\text{\tint{\tint{\tint{\tint{\ticl{\ticl{\ticl{\titrice{\tint{\text{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\text{\tint{\tint{\text{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\ticl{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tint{\tiint{\tiint{\tint{\tint{\tint{\tint{\tint{\tiil\tii}}}\tint{\tiin}\tit |

|                    |      |    |    | 1  | 1  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    |    | 0  | 0  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    | 0  | 0  | 1  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      | 0  | U  | 1  | 0  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    |    | 1  | 1  | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |      |    |    | 0  | 0  | 0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |