INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC02 September 1989

### TDA8417

### **GENERAL DESCRIPTION**

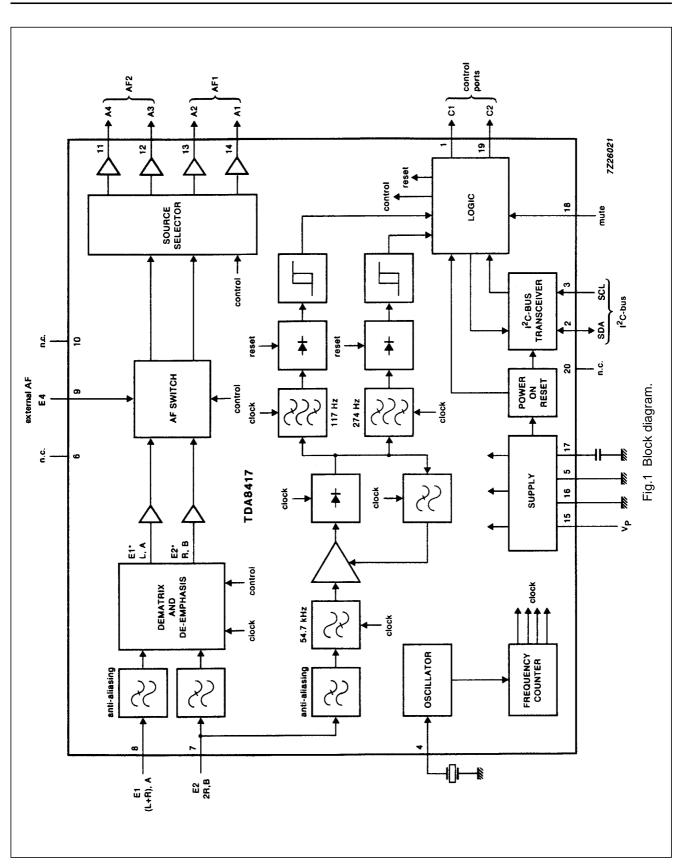

The TDA8417 is a processor of stereo/dual language signals (B/G-standard) for stereo sound television receivers and VTRs, using the switched-capacitor technique. The AF signals at the TDA8417 inputs must be "(L+R)/2" or "language A" on one channel and "R" or "language B" on the second channel (where L = left and R = right). The carrier frequency of the second channel is also modulated by an identification signal (stereo or dual sound). The device is controlled by a microcomputer via the two-line, bidirectional l<sup>2</sup>C-bus.

### Features

- Use of the switched-capacitor technique for signal processing

- Small amount of peripheral components

- Integrated anti-aliasing filters

- Low distortion AF signal handling

- Integrated de-emphasis with a time constant of 50 μs

- Two general purpose output ports

- Full ESD protection

| PARAMETER                                      | CONDITION             | SYMBOL           | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------------|-----------------------|------------------|------|------|------|------|

| Supply voltage (pin 15)                        |                       | VP               | _    | 12   | _    | V    |

| Supply current (pin 15)                        |                       | I <sub>P</sub>   | _    | 10   | _    | mA   |

| AF output signal (RMS value)                   |                       |                  |      |      |      |      |

| (pins 11 to 14)                                |                       | Vo               | _    | 2    | _    | V    |

| Weighted signal-to-noise                       |                       |                  |      |      |      |      |

| ratio of the AF output<br>signals (CCIR 468/3) |                       | (S+W)/W          | 70   | _    | _    | dB   |

| Crosstalk attenuation                          |                       |                  |      |      |      |      |

| stereo mode at                                 | f = 1 kHz             | $\alpha_{\rm S}$ | 40   | -    | -    | dB   |

| dual sound mode at                             | f = 40 Hz to 12.5 kHz | $\alpha_{DS}$    | 70   | -    | -    | dB   |

| Pilot signal input sensitivity                 |                       | Vi               | -    | 2.5  | -    | mV   |

| Total harmonic distortion                      |                       | THD              | _    | 0.1  | -    | %    |

### QUICK REFERENCE DATA

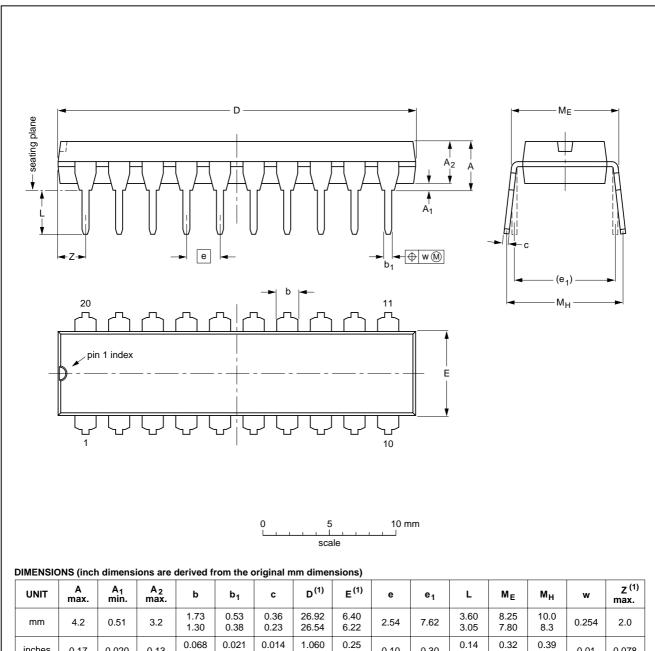

### PACKAGE OUTLINE

20-lead DIL; plastic (SOT146); SOT146-1; 1996 November 18

# TV and VTR stereo/dual sound processor with integrated filters and I<sup>2</sup>C-bus control

### September 1989

### PINNING

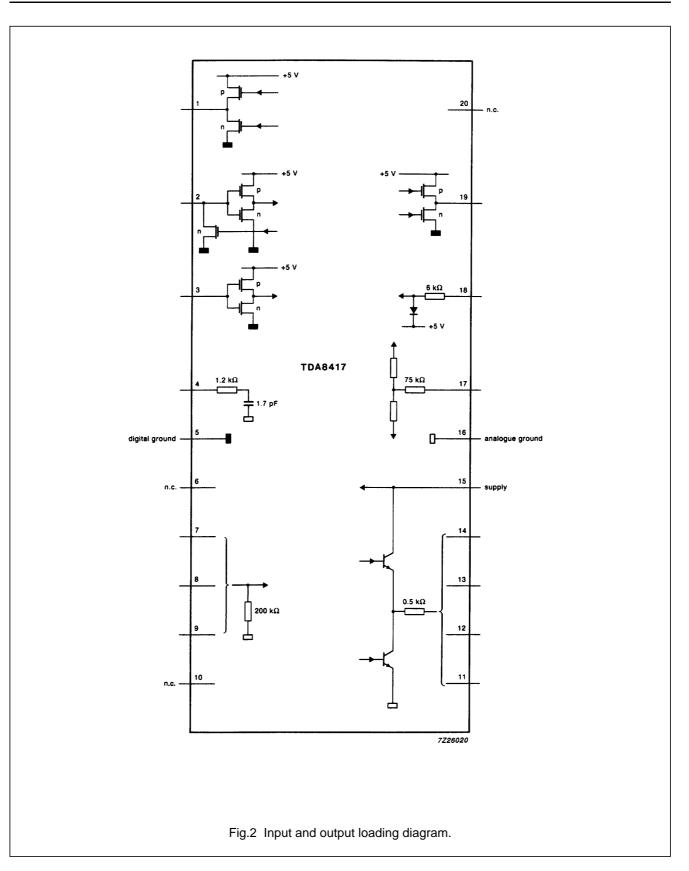

- 1 Control port C1

- 2 SDA, serial data line (I<sup>2</sup>C-bus)

- 3 SCL, serial clock line (I<sup>2</sup>C-bus)

- 4 Oscillator input (or quartz)

- 5 Digital ground (0 V)

- 6 Not connected, but reserved

- 7 Sound channel input AF2 (E2)

- 8 Sound channel input AF1 (E1)

- 9 External AF input (E4)

- 10 Not connected, but reserved

- 11 Output A4 AF 2 output

- 12 Output A3 AF 2 output

- 13 Output A2 AF 1 output

- 14 Output A1 AF 1 output

- 15 Supply voltage V<sub>P</sub>

- 16 Analogue ground (0 V)

- 17 Ripple rejection improvement

- 18 Mute input

- 19 Control port C2

- 20 Not connected, but reserved

### FUNCTIONAL DESCRIPTION

#### Anti-aliasing filters

Frequency band limitation is performed by a second order Sallen and Key low-pass filter inserted in the AF signal path and the identification circuit. This limitation is necessary because of the time-discrete signal processing needed to meet the Nyquist criterium.

#### Identification

To enable the identification of the transmitted AF signal (mono, stereo or dual sound), the carrier frequency of the second channel (E2) is also modulated by an identification signal. The identification signal is a 54.6875 kHz pilot carrier signal which is 50% amplitude modulated by either a 117.4 Hz signal for stereo transmission or by a 274.1 Hz signal for dual sound transmission.

The identification section of the circuit consists of a 54 kHz high-pass filter followed by a gain controlled amplifier with an AM demodulator. The total gain of the high-pass filter and the amplifier is approximately 56 dB. The demodulated identification signal is filtered by the identification band-pass filters, (117.4 Hz for stereo transmission, 274.1 Hz for dual sound transmission). The output from either filter is converted to a DC signal by a peak detector and the necessary hysteresis is performed by a Schmitt-trigger. The resultant DC output signals indicate the status of the transmitter (mono, stereo or dual sound).

TDA8417

### TDA8417

### **De-matrix and de-emphasis**

Depending on the results of the identification circuit (mono, stereo or dual sound) the AF signals at the inputs E1 and E2 are converted to the signals at E1\* and E2\* as listed in Table 1.

Table 1

Transmitter status <sup>(1)</sup>

| TRANSMITTER STATUS | E1       | E2 | E1*    | E2* |

|--------------------|----------|----|--------|-----|

| mono               | 0.7(L+R) | -  | 2(L+R) | -   |

| stereo             | 0.7(L+R) | 2R | 4L     | 4R  |

| dual sound         | 0.7A     | В  | 2A     | 2B  |

#### Note

- 1. L = left channel signal;

- R = right channel signal;

- A = first sound channel signal;

- B = second sound channel signal

This section of the circuit also performs the de-emphasis (50 µs time constant) with a high degree of accuracy.

### AF switch

The AF switch is used to switch to either the internal sound sources (E1\* or E1\* and E2\*) or, to the external sound source (E3 and E4) and is controlled via the  $l^2$ C-bus.

### Source selector

The source selector is used to connect the outputs from the AF switch to the outputs A1 to A4 as illustrated by Table 5. The selector is controlled via the  $l^2C$ -bus.

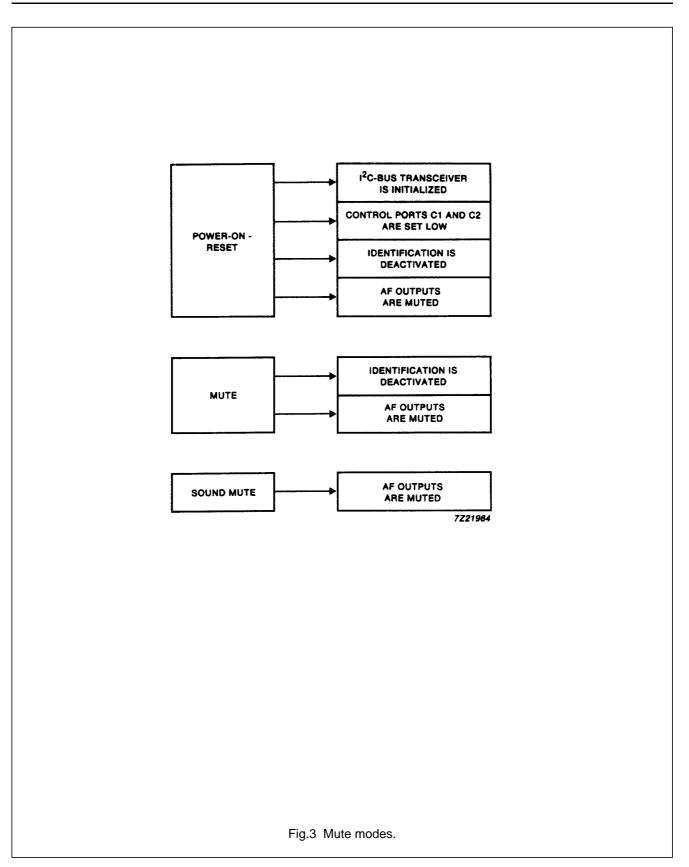

### Muting

In this mode the AF outputs A1 to A4 are muted, and the identification circuit is deactivated (mono). The muting is active after power-on reset or as a result of user control (via the mute input and bit CR3 of the control byte of the mute and port control register; see Table 4).

### Sound mute

If the switch register is set to (00) hex, (sound mute) only the AF outputs are muted, the identification circuit is still active and can be read (status register) via the I<sup>2</sup>C-bus.

### TDA8417

### Power-on reset

The following actions are carried out by the internal power-on reset when it is active:

- The AF outputs are muted

- The identification circuit is deactivated (mono)

- The control ports (C1 and C2) are set LOW

- The I<sup>2</sup>C-bus transceiver is initialized

When the power-on reset becomes passive the following occurs:

- The AF outputs are kept in the mute state until the contents of the switch register are changed from (00) hex via the  $I^2C$ -bus

- The identification circuit is activated

- The control ports are LOW until the mute and control port register is changed (CR bits 10, 11, 20 and 21)

- The I<sup>2</sup>C-bus transceiver is activated

# TV and VTR stereo/dual sound processor with integrated filters and $I^2C$ -bus control

### Control ports

The general purpose control ports C1 and C2 can be set to LOW, HIGH or high impedance via the I<sup>2</sup>C-bus.

#### I<sup>2</sup>C-bus receiver and data handling

Bus specification

The TDA8417 is controlled, via the bidirectional 2-line  $l^2$ C-bus, by a microcomputer. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

When the bus is free both lines are HIGH. The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. The set up and hold times are specified in the CHARACTERISTICS.

A HIGH-to-LOW transition of the SDA line while SCL is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the SDA line while SCL is HIGH is defined as the stop condition (P). The bus receiver will be reset on the reception of a start condition. The bus is considered to be busy after the start condition. The bus is considered to be free again after a stop condition.

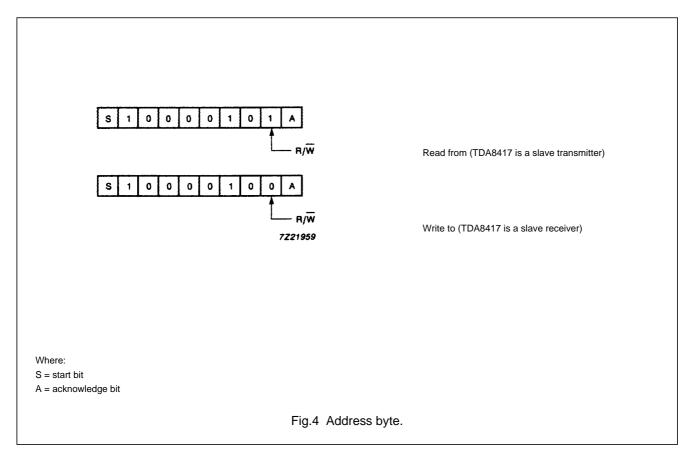

### The I<sup>2</sup>C-BUS PROTOCOL OF THE TDA8417

The TDA8417 is controlled by a microcomputer and can be written to or read from via the I<sup>2</sup>C-bus.

The first byte is the address and determines whether the TDA8417 is to be read from (status register) or written to (switch register or mute and port control register).

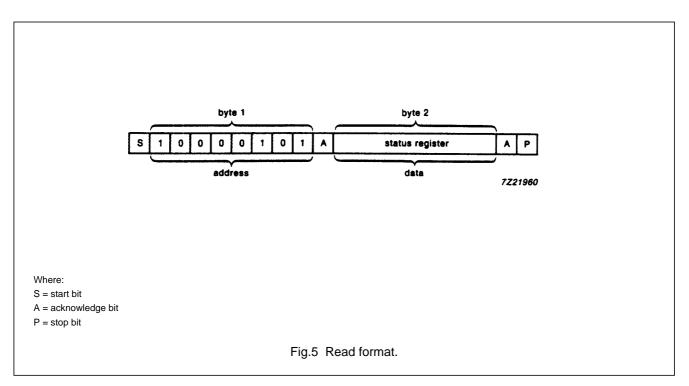

### Reading the TDA8417

Reading the TDA8417 means reading the status register and the data stream will have the format as illustrated in Fig.5 below.

The second byte, the contents of the status register, is defined by Table 2.

### Table 2 Status register

| D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------|----|----|----|----|----|----|----|

| PONRES | ST | DS | 0  | 0  | 0  | 0  | 0  |

### Where:

| PONRES | =   | power on reset                                              |

|--------|-----|-------------------------------------------------------------|

|        | 1 = | power on reset active after switching on or power breakdown |

|        | 0 = | after reading the status register                           |

| ST     | =   | stereo transmission                                         |

| DS     | =   | dual sound transmission                                     |

The truth table for the ST and DS bits is provided by Table 3.

| ST | DS | DEFINITION              |

|----|----|-------------------------|

| 0  | 0  | mono transmission       |

| 0  | 1  | dual sound transmission |

| 1  | 0  | stereo transmission     |

TDA8417

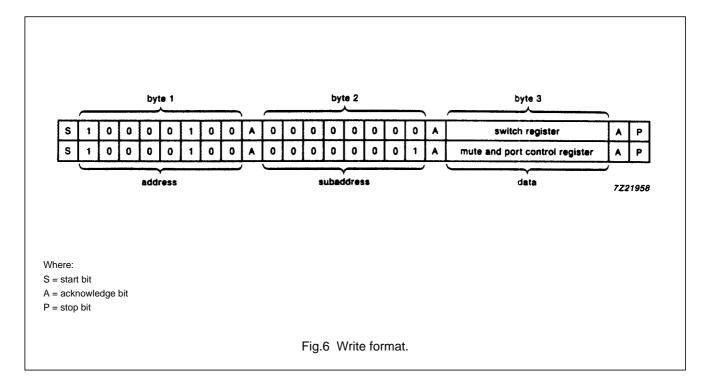

### Writing to the TDA8417

Writing to the TDA8417 means, writing to either the switch register or the mute and port control register. Which one is to be addressed is defined by the subaddress (the second byte) as illustrated by Fig.6 below. The third byte contains the information to be stored in the specified register.

Table 4 defines the contents of the mute and port control register.

Table 4

Mute and port control register <sup>(1)</sup>

| D7 | D6 | D5 | D4<br>CR3 | D3<br>CR21 | D2<br>CR20 | D1<br>CR11 | D0<br>CR10 | DEFINITION                                  |

|----|----|----|-----------|------------|------------|------------|------------|---------------------------------------------|

| Х  | Х  | Х  |           |            |            | 0          | 0          | control port C1 = LOW                       |

| Х  | X  | X  |           |            |            | 0          | 1          | control port C1 = HIGH                      |

| Х  | X  | X  |           |            |            | 1          | X          | control port C1 = high impedance            |

| Х  | X  | X  |           | 0          | 0          |            |            | control port C2 = LOW                       |

| Х  | X  | x  |           | 0          | 1          |            |            | control port C2 = HIGH                      |

| Х  | X  | x  |           | 1          | X          |            |            | control port C2 = high impedance            |

| Х  | X  | x  | 0         |            |            |            |            | mute is active when pin 18 is LOW (default) |

| Х  | X  | x  | 1         |            |            |            |            | mute is active when pin 18 is HIGH          |

### Note

1. X = don't care

# TV and VTR stereo/dual sound processor with integrated filters and $I^2C$ -bus control

Table 5 defines the contents of the switch register.

### Table 5 Switch register

| SWITCH     |    | INP | UT |    | OUTF   | TUY         |    |    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (HEX) |

|------------|----|-----|----|----|--------|-------------|----|----|----|----|----|----|----|----|----|----|-------|

| REGISTER   |    | E1  | E2 | E4 | A1     | A1 A2 A3 A4 |    |    |    |    |    |    |    |    |    |    |       |

| sound mute | _  | _   | _  | _  | no sig | Inal        |    |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (00)  |

| mono       | М  | М   | Μ  | _  | М      | М           | М  | М  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | (10)  |

|            | St | L*  | R  | _  | L*     | L*          | L* | L* | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | (10)  |

| stereo     | St | L*  | R  | _  | L      | R           | L  | R  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | (2A)  |

| sound A    | DS | А   | В  | _  | A      | А           | А  | А  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | (10)  |

| sound B    | DS | А   | В  | _  | В      | В           | В  | В  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | (1F)  |

| dual sound | DS | А   | В  | _  | A      | А           | В  | В  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | (1C)  |

|            | DS | А   | В  | _  | В      | В           | А  | А  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | (13)  |

| dual sound | DS | А   | В  | _  | A      | В           | А  | А  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | (12)  |

| mix        | DS | А   | В  | _  | A      | А           | А  | В  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | (18)  |

|            | DS | А   | В  | _  | A      | В           | А  | В  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | (1A)  |

|            | DS | А   | В  | _  | в      | В           | А  | В  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | (1B)  |

|            | DS | А   | В  | _  | A      | В           | В  | В  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | (1E)  |

| external   | _  | -   | _  | E4 | E4     | E4          | E4 | E4 | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | (7F)  |

#### Where:

| М  | = | mono       |

|----|---|------------|

| St | = | stereo     |

| DS | = | dual sound |

| R  | = | right      |

| L  | = | left       |

| L* | = | (L + R)/2  |

| А  | = | sound A    |

B = sound B

### TDA8417

### RATINGS

Limiting values in accordance with Absolute Maximum System (IEC 134)

| PARAMETER                                      | SYMBOL              | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------------|---------------------|------|------|------|------|

| Supply voltage <sup>(1)</sup>                  | $V_{P} = V_{15-16}$ | -    | -    | 13.2 | V    |

| Output current                                 |                     |      |      |      |      |

| pins 11, 12, 13, 14                            | Io                  | -    | _    | 10   | mA   |

| pins 1 and 19 (sink)                           | I <sub>O</sub>      | -    | -    | 7    | mA   |

| (source)                                       | -I <sub>O</sub>     | -    | _    | 3    | mA   |

| Input voltage (not pin 18)                     | VI                  | 0    | -    | VP   | V    |

| Input voltage pin 18                           | $V_{I} = V_{18-16}$ | -    | -    | 7    | V    |

| Output voltage                                 | Vo                  | 0    | _    | VP   | V    |

| Total power dissipation                        | P <sub>tot</sub>    | -    | _    | 1    | W    |

| ESD protection (each pin) (0 $\Omega$ /200 pF) | V <sub>es</sub>     | 500  | -    | -    | V    |

| Operating ambient temperature range            | T <sub>amb</sub>    | 0    | _    | + 70 | °C   |

| Storage temperature range                      | T <sub>stg</sub>    | -40  | _    | +150 | °C   |

### Note

1. Supply voltage may be applied only when both pins 5 and 15 are connected to ground.

### TDA8417

### CHARACTERISTICS

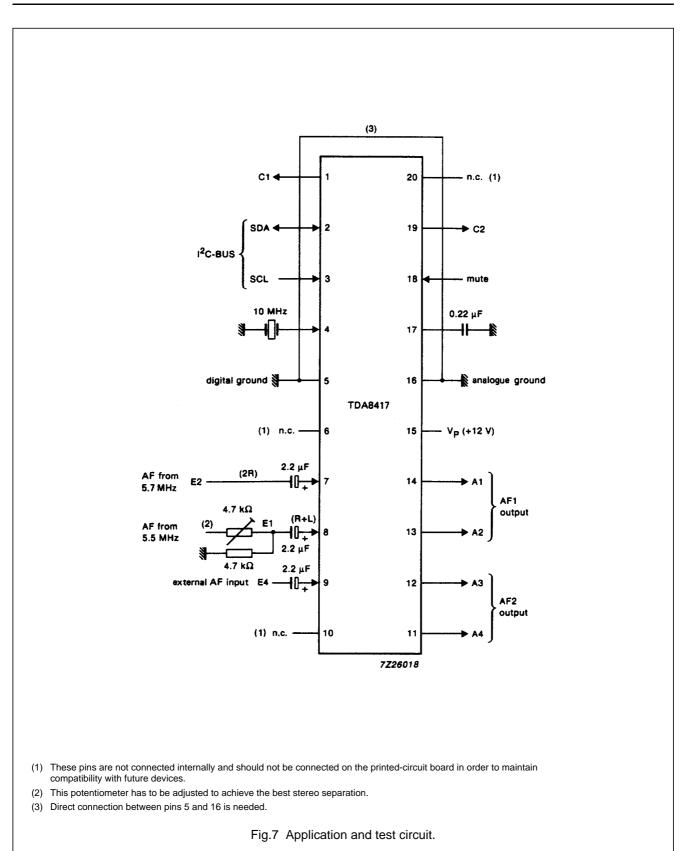

$V_P = 12$  V;  $T_{amb} = 25$  °C. Measurement conditions (see Fig.7): reference level is 1 V (RMS); test frequency = 3.183 kHz; noise measurement in accordance with DIN 45405, CCIR 468-3; oscillator frequency = 10 MHz; pre-emphasis time constant = 50  $\mu$ s.

| PARAMETER              | CONDITIONS | SYMBOL               | MIN. | TYP. | MAX. | UNIT |

|------------------------|------------|----------------------|------|------|------|------|

| Supplies               |            |                      |      |      |      |      |

| Supply voltage         |            | $V_{P} = V_{15-16}$  | 10.8 | 12   | 13.2 | V    |

| Supply current         |            | $I_{P} = I_{15}$     | _    | 10   | -    | mA   |

| DC levels              |            |                      |      |      |      |      |

| pins 7 - 14 and 17     |            | V <sub>n-16</sub>    | _    | 3.25 | -    | V    |

| pin 4                  |            | V <sub>4-5</sub>     | -    | 2    | -    | V    |

| Bus transceiver        |            |                      |      |      |      |      |

| Clock frequency        |            |                      |      |      |      |      |

| (I <sup>2</sup> C-bus) | note 1     | f <sub>CLK</sub>     | 0.7  | _    | 100  | kHz  |

| Clock SCL (pin 3)      |            |                      |      |      |      |      |

| Input voltage LOW      |            | VIL                  | -0.3 | _    | 1.5  | V    |

| Input voltage HIGH     |            | VIH                  | 3    | _    | 5    | V    |

| Timing LOW period      |            | t <sub>LOW</sub>     | 4.7  | -    | -    | μs   |

| Timing HIGH period     |            | t <sub>HIGH</sub>    | 4    | -    | _    | μs   |

| Rise time              |            | t <sub>r</sub>       | _    | -    | 1    | μs   |

| Fall time              |            | t <sub>f</sub>       | _    | -    | 0.3  | μs   |

| Input current LOW      |            | -I <sub>IL</sub>     | _    | -    | 10   | μA   |

| Input current HIGH     |            | I <sub>IH</sub>      | -    | -    | 10   | μA   |

| Data SDA (pin 2)       |            |                      |      |      |      |      |

| Input voltage LOW      |            | VIL                  | -0.3 | -    | 1.5  | V    |

| Input voltage HIGH     |            | VIH                  | 3    | _    | 5    | V    |

| Rise time              |            | tr                   | _    | -    | 1    | μs   |

| Fall time              |            | t <sub>f</sub>       | -    | -    | 0.3  | μs   |

| Data set-up time       |            | t <sub>SU; DAT</sub> | 0.25 | -    | -    | μs   |

| Input current LOW      |            | -I <sub>IL</sub>     | -    | -    | 10   | μA   |

| Input current HIGH     |            | I <sub>IH</sub>      | -    | -    | 10   | μA   |

| Output current LOW     |            | I <sub>OL</sub>      | 3    | -    | -    | mA   |

| Mute port (pin 18)     |            |                      |      |      |      |      |

| Input voltage LOW      | note 2     | VIL                  | -0.3 | -    | 1.5  | V    |

| Input voltage HIGH     | note 2     | VIH                  | 3    | -    | 5    | V    |

### TDA8417

| PARAMETER                                      | CONDITIONS   | SYMBOL           | MIN. | TYP. | MAX. | UNIT        |

|------------------------------------------------|--------------|------------------|------|------|------|-------------|

| Control ports                                  |              |                  |      |      |      |             |

| (pins 1 and 19)                                |              |                  |      |      |      |             |

| Output voltage LOW                             | note 3       | V <sub>OL</sub>  | _    | _    | 0.5  | V           |

| Output voltage HIGH                            | note 3       | V <sub>OH</sub>  | 4.5  | _    | 5    | V           |

| Output impedance                               | 3-state      | Zo               | 1    | _    | _    | MΩ          |

| Output current LOW                             |              | I <sub>OL</sub>  | 1    | _    | _    | mA          |

| Output current HIGH                            |              | -I <sub>OH</sub> | 1    | _    | _    | mA          |

| AF stages and identification<br>(pins 7 to 14) |              |                  |      |      |      |             |

| Input impedance                                |              |                  |      |      |      |             |

| (pins 7 to 9)                                  |              | Zi               | 150  | 200  | _    | kΩ          |

| Input voltage E1                               |              | VI               | _    | _    | 0.7  | V           |

| Input voltage E2                               |              | V                | _    | _    | 1    | V           |

| Input voltage E2 for identification            |              |                  |      |      |      |             |

| active (RMS value)                             | note 4       | Vi               | 2.5  | -    | -    | mV          |

| Voltage gain 7-15/output                       | note 5       | Gv               | 5.9  | 6    | 6.1  | dB          |

| Voltage gain 8-15/output                       | note 5       | G <sub>v</sub>   | 8.9  | 9    | 9.1  | dB          |

| Voltage gain                                   |              |                  |      |      |      |             |

| 9-15/output                                    |              | Gv               | -0.1 | 0    | 0.1  | dB          |

| Crosstalk attenuation                          | notes 6 to 8 |                  |      |      |      |             |

| dual mode                                      |              | $\alpha_{ds}$    | 70   | 75   | -    | dB          |

| stereo mode                                    |              | α <sub>s</sub>   | 30   | 50   | -    | dB          |

| Output impedance                               |              |                  |      |      |      |             |

| (pins 11 to 14)                                |              | Zo               | 400  | 500  | 600  | Ω           |

| De-emphasis time                               |              |                  |      |      |      |             |

| constant                                       | note 9       |                  | 49.5 | 50   | 50.5 | μs          |

| Frequency response<br>Total harmonic           | note 6       | Δf               | -1   | -    | 1    | dB          |

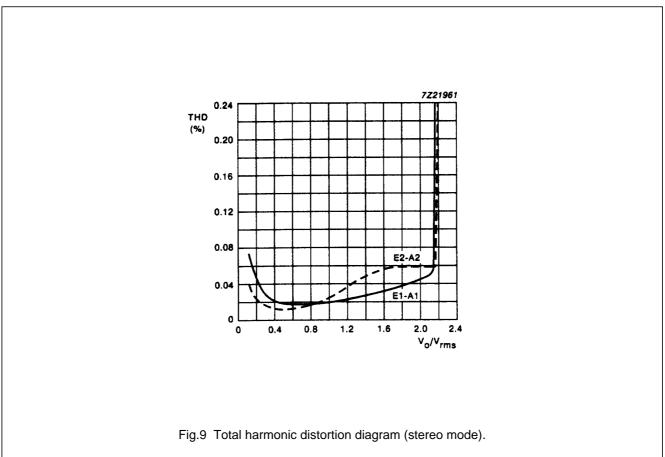

| distortion                                     | note 10      | THD              | -    | _    | 0.2  | %           |

| Capacitive load                                |              |                  |      |      |      |             |

| (pins 11 to 14)                                |              | CL               | _    | _    | 1.5  | nF          |

| Output signal                                  |              |                  |      |      |      |             |

| (RMS value)                                    |              |                  |      |      |      |             |

| (pins 11 to 14)                                | THD ≤ 0.2%   | Vo               | -    | -    | 2    | V           |

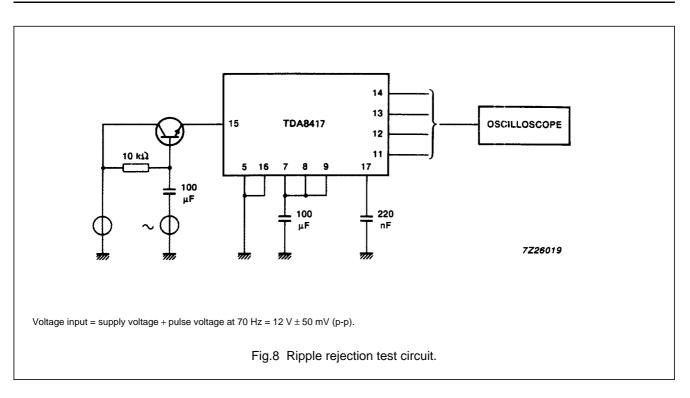

| Ripple rejection                               | note 11      | RR               | 50   | 66   | -    | dB          |

| Noise from I <sup>2</sup> C-bus                |              | NR               | -    | -    | -80  | dB          |

| Signal-to-noise ratio                          |              | (S+W)/W          | 70   | -    | -    | dBV<br>CCIR |

### TDA8417

| PARAMETER                                    | CONDITIONS | SYMBOL           | MIN. | TYP.        | MAX. | UNIT |

|----------------------------------------------|------------|------------------|------|-------------|------|------|

| Signal suppression                           |            |                  |      |             |      |      |

| during mute                                  | note 6     | SS               | 70   | 75          | -    | dB   |

| Change of output                             |            |                  |      |             |      |      |

| DC voltage level<br>between any two<br>modes |            |                  | _    | _           | 30   | mV   |

| Oscillator                                   |            |                  |      |             |      |      |

| Oscillator frequency                         |            | f <sub>OSC</sub> | -    | 10          | _    | MHz  |

| External oscillator                          |            |                  |      |             |      |      |

| signal (RMS value)                           |            | V <sub>4-5</sub> | 1.7  | _           | _    | V    |

| Quartz series resistor                       |            | R1               | -    | _           | 100  | Ω    |

| Impedance                                    |            | Zi               | -    | -1.2 + j9.3 | -    | kΩ   |

| Capacitance                                  |            | C <sub>OSC</sub> | -    | 1.7         | -    | pF   |

### Notes to the characteristics

- 1. Full specification of I<sup>2</sup> C-bus will be supplied on request.

- 2. Programmable mute state. If the CR3 bit of the mute and port control register is LOW, the mute is active LOW; if it is HIGH, the mute input is active HIGH.

- 3. Output current  $I_0 \approx 1$  mA.

- 4. Unmodulated.

- 5.  $f = 400 \text{ Hz}; \text{ R}_{L} = 1 \text{ M}\Omega.$

- 6. 40 Hz  $\leq$  f  $\leq$  15 kHz.

- In dual mode: A(B)-signal into B(A)-channel.

In stereo mode: R-signal into left, L-signal = 0, reference is 1 V RMS.

- 8. Source impedance  $|Z_S| < 1 \text{ k}\Omega$ .

- 9. Equivalent to an output level of -3 dB at f = 3.183 kHz.

- 10. V<sub>o</sub> = 1 V RMS; f =1 kHz.

- 11. Test circuit see Fig.7.

## TV and VTR stereo/dual sound processor with integrated filters and I<sup>2</sup>C-bus control

# TV and VTR stereo/dual sound processor with integrated filters and I<sup>2</sup>C-bus control

### **Philips Semiconductors**

## TV and VTR stereo/dual sound processor with integrated filters and I<sup>2</sup>C-bus control

### PACKAGE OUTLINE

### DIP20: plastic dual in-line package; 20 leads (300 mil)

#### Note

inches

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

0.051

0.015

0.009

0.13

0.020

0.17

| OUTLINE  | REFERENCES |       |       | EUROPEAN | ISSUE DATE |                                 |

|----------|------------|-------|-------|----------|------------|---------------------------------|

| VERSION  | IEC        | JEDEC | EIAJ  |          | PROJECTION | ISSUE DATE                      |

| SOT146-1 |            |       | SC603 |          |            | <del>92-11-17</del><br>95-05-24 |

1.045

0.24

0.10

0.30

0.12

0.31

SOT146-1

0.078

0.01

0.33

### TDA8417

### SOLDERING

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"IC Package Databook"* (order code 9398 652 90011).

### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact

with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg\,max}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

### **Repairing soldered joints**

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### DEFINITIONS

| Data sheet status                                             |                                                                                                                                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Objective specification                                       | This data sheet contains target or goal specifications for product development.                                                                                                                                                                                                                                                                 |  |  |

| Preliminary specification                                     | This data sheet contains preliminary data; supplementary data may be published la                                                                                                                                                                                                                                                               |  |  |

| Product specification                                         | This data sheet contains final product specifications.                                                                                                                                                                                                                                                                                          |  |  |

| Limiting values                                               |                                                                                                                                                                                                                                                                                                                                                 |  |  |

| more of the limiting values r<br>of the device at these or at | accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or<br>nay cause permanent damage to the device. These are stress ratings only and operation<br>any other conditions above those given in the Characteristics sections of the specification<br>imiting values for extended periods may affect device reliability. |  |  |

| Application information                                       |                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Where application informati                                   | on is given, it is advisory and does not form part of the specification.                                                                                                                                                                                                                                                                        |  |  |

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.