# High Speed/High Temperature Dual Digital Isolators

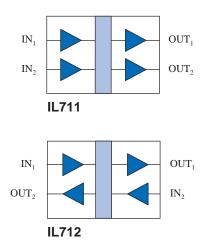

#### **Functional Diagrams**

#### **Features**

- +5 V/+3.3 V CMOS / TTL Compatible

- High Speed: 150 Mbps Typical (IL711S/IL712S)

- High Temperature: -40°C to +125°C (IL711T/IL712T)

- 2500 V<sub>RMS</sub> Isolation (1 min.)

- 300 ps Typical Pulse Width Distortion (IL711S/IL712S)

- 4 ns Typical Propagation Delay Skew

- 10 ns Typical Propagation Delay

- 30 kV/µs Typical Common Mode Transient Immunity

- 2 ns Channel-to-Channel Skew

- 8-pin MSOP, SOIC, and PDIP Packages

- UL1577 and IEC 61010-2001 Approval

#### Applications

- ADCs and DACs

- Digital Fieldbus

- RS-485 and RS-422

- Multiplexed Data Transmission

- Data Interfaces

- Board-to-Board Communication

- Digital Noise Reduction

- Operator Interface

- Ground Loop Elimination

- Peripheral Interfaces

- Serial Communication

- Logic Level Shifting

#### **Description**

NVE's IL700 family of high-speed digital isolators are CMOS devices manufactured with NVE's patented\* IsoLoop<sup>®</sup> spintronic Giant Magnetoresistive (GMR) technology. The IL711S and IL712S are the world's fastest two-channel isolators, with a 150 Mbps typical data rate for both channels.

The symmetric magnetic coupling barrier provides a typical propagation delay of only 10 ns and a pulse width distortion as low as 300 ps (0.3 ns), achieving the best specifications of any isolator. Typical transient immunity of 30 kV/ $\mu$ s is unsurpassed. The IL711 has two transmit channels; the IL712 has one transmit and one receive channel. The IL712 operates full duplex, making it ideal for many fieldbus applications, including PROFIBUS.

The IL711 and IL712 are available in 8-pin MSOP, SOIC, and PDIP packages. Standard and S-Grade parts are specified over a temperature range of  $-40^{\circ}$ C to  $+100^{\circ}$ C; T-Grade parts are specified over a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

IsoLoop is a registered trademark of NVE Corporation. \*U.S. Patent numbers 5,831,426; 6,300,617 and others.

# Absolute Maximum Ratings

| Parameters                                                    | Symbol             | Min. | Тур. | Max.           | Units | Test Conditions |

|---------------------------------------------------------------|--------------------|------|------|----------------|-------|-----------------|

| Storage Temperature                                           | Ts                 | -55  |      | 150            | °C    |                 |

| Ambient Operating Temperature <sup>(1)</sup><br>IL711T/IL712T | T <sub>A</sub>     | -55  |      | 125<br>135     | °C    |                 |

| Supply Voltage                                                | $V_{DD1}, V_{DD2}$ | -0.5 |      | 7              | V     |                 |

| Input Voltage                                                 | VI                 | -0.5 |      | $V_{DD} + 0.5$ | V     |                 |

| Output Voltage                                                | Vo                 | -0.5 |      | $V_{DD} + 0.5$ | V     |                 |

| Output Current Drive                                          | Io                 |      |      | 10             | mA    |                 |

| Lead Solder Temperature                                       |                    |      |      | 260            | °C    | 10 sec.         |

| ESD                                                           |                    |      | 2    |                | kV    | HBM             |

#### **Recommended Operating Conditions**

| Parameters                       | Symbol             | Min. | Тур. | Max.            | Units | Test Conditions |

|----------------------------------|--------------------|------|------|-----------------|-------|-----------------|

| Ambient Operating Temperature    |                    |      |      |                 |       |                 |

| IL711/IL712 and IL711S/IL712S    | T <sub>A</sub>     | -40  |      | 100             | °C    |                 |

| IL711T/IL712T                    |                    | -40  |      | 125             | °C    |                 |

| Supply Voltage                   | $V_{DD1}, V_{DD2}$ | 3.0  |      | 5.5             | V     |                 |

| Logic High Input Voltage         | V <sub>IH</sub>    | 2.4  |      | V <sub>DD</sub> | V     |                 |

| Logic Low Input Voltage          | V <sub>IL</sub>    | 0    |      | 0.8             | V     |                 |

| Input Signal Rise and Fall Times | $t_{IR}, t_{IF}$   |      |      | 1               | μs    |                 |

#### **Insulation Specifications**

| Parameters        | Symbol | Min. | Тур.                  | Max. | Units                 | Test Conditions              |

|-------------------|--------|------|-----------------------|------|-----------------------|------------------------------|

| Creepage Distance |        |      |                       |      |                       |                              |

| MSOP              |        | 3.01 |                       |      | mm                    |                              |

| SOIC              |        | 4.03 |                       |      | mm                    |                              |

| PDIP              |        | 7.04 |                       |      | mm                    |                              |

| Leakage Current   |        |      | 0.2                   |      | μΑ                    | 240 V <sub>RMS</sub> , 60 Hz |

| Barrier Impedance |        |      | >10 <sup>14</sup>   3 |      | $\Omega \parallel pF$ |                              |

#### **Package Characteristics**

| Parameters                                | Symbol            | Min. | Тур. | Max. | Units | Test Conditions                                |

|-------------------------------------------|-------------------|------|------|------|-------|------------------------------------------------|

| Capacitance (Input–Output) <sup>(5)</sup> | C <sub>I-O</sub>  |      | 2    |      | pF    | f = 1 MHz                                      |

| Thermal Resistance                        |                   |      |      |      |       |                                                |

| MSOP                                      | $\theta_{JC}$     |      | 168  |      | °C/W  | Thermonounle et center                         |

| SOIC                                      | $\theta_{\rm JC}$ |      | 144  |      | °C/W  | Thermocouple at center<br>underside of package |

| PDIP                                      | $\theta_{JC}$     |      | 54   |      | °C/W  | underside of package                           |

| Package Power Dissipation                 | P <sub>PD</sub>   |      |      | 150  | mW    | $f = 1 \text{ MHz}, V_{DD} = 5 \text{ V}$      |

## Safety and Approvals

#### IEC61010-1

TUV Certificate Numbers: N1502812, N1502812-101

#### **Classification as Reinforced Insulation**

|                  |         | Pollution | Material         | Max. Working         |

|------------------|---------|-----------|------------------|----------------------|

| Model            | Package | Degree    | Group            | Voltage              |

| IL711-1; IL712-1 | MSOP    |           | Pending Approval |                      |

| IL711-2; IL712-2 | PDIP    | II        | III              | 300 V <sub>RMS</sub> |

| IL711-3; IL712-3 | SOIC    | II        | III              | 150 V <sub>RMS</sub> |

### UL 1577

Component Recognition Program File Number: E207481 Rated  $2500V_{RMS}$  for 1 minute

#### Soldering Profile

Per JEDEC J-STD-020C, MSL=2

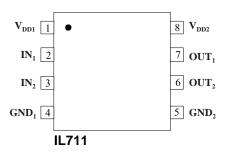

# **IL711 Pin Connections**

| 1 | V <sub>DD1</sub> | Supply voltage                     |

|---|------------------|------------------------------------|

| 2 | IN <sub>1</sub>  | Data in, channel 1                 |

| 3 | IN <sub>2</sub>  | Data in, channel 2                 |

| 4 | GND <sub>1</sub> | Ground return for V <sub>DD1</sub> |

| 5 | GND <sub>2</sub> | Ground return for V <sub>DD2</sub> |

| 6 | OUT <sub>2</sub> | Data out, channel 2                |

| 7 | OUT <sub>1</sub> | Data out, channel 1                |

| 8 | V <sub>DD2</sub> | Supply voltage                     |

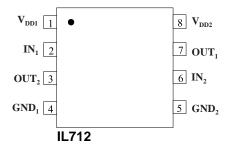

# **IL712 Pin Connections**

| 1 | V <sub>DD1</sub> | Supply voltage                     |

|---|------------------|------------------------------------|

| 2 | IN <sub>1</sub>  | Data in, channel 1                 |

| 3 | OUT <sub>2</sub> | Data out, channel 2                |

| 4 | GND <sub>1</sub> | Ground return for V <sub>DD1</sub> |

| 5 | GND <sub>2</sub> | Ground return for V <sub>DD2</sub> |

| 6 | IN <sub>2</sub>  | Data in, channel 2                 |

| 7 | OUT <sub>1</sub> | Data out, channel 1                |

| 8 | V <sub>DD2</sub> | Supply voltage                     |

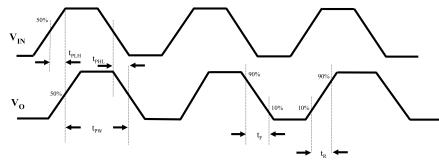

# Timing Diagram

| Legen            | d                              |

|------------------|--------------------------------|

| t <sub>PLH</sub> | Propagation Delay, Low to High |

| t <sub>PHL</sub> | Propagation Delay, High to Low |

| t <sub>PW</sub>  | Minimum Pulse Width            |

| t <sub>R</sub>   | Rise Time                      |

| t <sub>F</sub>   | Fall Time                      |

# 3.3 Volt Electrical Specifications

Electrical specifications are  $T_{min}$  to  $T_{max}$  unless otherwise stated.

| Parameters                                      | Symbol              | Min.                      | Тур.                               | Max.                    | Units  | Test Conditions                     |

|-------------------------------------------------|---------------------|---------------------------|------------------------------------|-------------------------|--------|-------------------------------------|

|                                                 |                     | DC Specific               | cations                            |                         |        |                                     |

| Input Quiescent Supply Current                  |                     |                           |                                    |                         |        |                                     |

| IL711                                           | т                   |                           | 8                                  | 10                      | μA     |                                     |

| IL712                                           | I <sub>DD1</sub>    |                           | 1.5                                | 2                       | mA     |                                     |

| Output Quiescent Supply Current                 |                     |                           |                                    |                         |        |                                     |

| IL711                                           | т                   |                           | 3.3                                | 4                       | mA     |                                     |

| IL712                                           | I <sub>DD2</sub>    |                           | 1.5                                | 2                       | mA     |                                     |

| Logic Input Current                             | II                  | -10                       |                                    | 10                      | μΑ     |                                     |

| Logic High Output Voltage                       | V <sub>OH</sub>     | $V_{DD} - 0.1$            | V <sub>DD</sub>                    |                         | v      | $I_0 = -20 \ \mu A, V_I = V_{IH}$   |

| Logie ingli o'alpat + onage                     | ·On                 | $0.8 \ge V_{DD}$          | 0.9 x V <sub>DD</sub>              |                         |        | $I_0 = -4 \text{ mA}, V_I = V_{IH}$ |

| Logic Low Output Voltage                        | V <sub>OL</sub>     |                           | 0                                  | 0.1                     | v      | $I_0 = 20 \ \mu A, V_I = V_{IL}$    |

| Logie Low Output Voluge                         | + OL                |                           | 0.5                                | 0.8                     | ·      | $I_0 = 4 \text{ mA}, V_I = V_{IL}$  |

|                                                 | S                   | Switching Spee            | cifications                        |                         |        |                                     |

| Maximum Data Rate                               |                     |                           |                                    |                         |        |                                     |

| IL711/IL712 and IL711T/IL712T                   |                     | 100                       | 110                                |                         | Mbps   | $C_L = 15 \text{ pF}$               |

| IL711S and IL712S                               |                     | 130                       | 140                                |                         | Mbps   | $C_L = 15 \text{ pF}$               |

| Pulse Width <sup>(7)</sup>                      | PW                  | 10                        | 7.5                                |                         | ns     | 50% Points, Vo                      |

| Propagation Delay Input to Output               | t <sub>PHL</sub>    |                           | 12                                 | 18                      | ns     | $C_{L} = 15 \text{ pF}$             |

| (High to Low)                                   | PHL                 |                           | 12                                 | 10                      | 115    | $C_L = 15 \text{ pr}$               |

| Propagation Delay Input to Output               | t <sub>PLH</sub>    |                           | 12                                 | 18                      | ns     | $C_{L} = 15 \text{ pF}$             |

| (Low to High)                                   | PLH                 |                           | 12                                 | 10                      | 115    | 0L = 15 pr                          |

| Pulse Width Distortion <sup>(2)</sup>           |                     |                           |                                    |                         |        |                                     |

| IL711/IL712 and IL711T/IL712T                   | PWD                 |                           | 2                                  | 3                       | ns     | $C_L = 15 \text{ pF}$               |

| IL711S and IL712S                               |                     |                           | 1                                  | 3                       |        |                                     |

| Propagation Delay Skew <sup>(3)</sup>           | t <sub>PSK</sub>    |                           | 4                                  | 6                       | ns     | $C_L = 15 \text{ pF}$               |

| Output Rise Time (10%–90%)                      | t <sub>R</sub>      |                           | 2                                  | 4                       | ns     | $C_L = 15 \text{ pF}$               |

| Output Fall Time (10%–90%)                      | t <sub>F</sub>      |                           | 2                                  | 4                       | ns     | $C_L = 15 \text{ pF}$               |

| Common Mode Transient Immunity                  | $ CM_{H} , CM_{L} $ | 20                        | 30                                 |                         | kV/μs  | $V_{\rm CM} = 300  \rm V$           |

| (Output Logic High or Logic Low) <sup>(4)</sup> |                     | 20                        | 50                                 |                         | κ ν/μ5 | • <sub>CM</sub> = 500 •             |

| Channel-to-Channel Skew                         | t <sub>csk</sub>    |                           | 2                                  | 3                       | ns     | $C_L = 15 \text{ pF}$               |

| Dynamic Power Consumption <sup>(6)</sup>        |                     |                           | 140                                | 240                     | µA/MHz | per channel                         |

|                                                 | Magnetic Field I    | mmunity <sup>(8)</sup> (V | $V_{\rm DD2} = 3V,  3V < 10^{-10}$ | V <sub>DD1</sub> <5.5V) |        |                                     |

| Power Frequency Magnetic Immunity               | H <sub>PF</sub>     | 1000                      | 1500                               |                         | A/m    | 50Hz/60Hz                           |

| Pulse Magnetic Field Immunity                   | H <sub>PM</sub>     | 1800                      | 2000                               |                         | A/m    | $t_p = 8\mu s$                      |

| Damped Oscillatory Magnetic Field               | H <sub>OSC</sub>    | 1800                      | 2000                               |                         | A/m    | 0.1Hz – 1MHz                        |

| Cross-axis Immunity Multiplier <sup>(9)</sup>   | K <sub>X</sub>      |                           | 2.5                                |                         | T      |                                     |

# **5 Volt Electrical Specifications**

Electrical specifications are  $T_{min}$  to  $T_{max}$  unless otherwise stated.

| Parameters                                      | Symbol             | Min.                                  | Тур.                  | Max.             | Units  | Test Conditions                     |

|-------------------------------------------------|--------------------|---------------------------------------|-----------------------|------------------|--------|-------------------------------------|

|                                                 |                    | DC Specifie                           | cations               |                  | -      | ·                                   |

| Input Quiescent Supply Current                  |                    |                                       |                       |                  |        |                                     |

| IL711                                           | т                  |                                       | 10                    | 15               | μΑ     |                                     |

| IL712                                           | - I <sub>DD1</sub> |                                       | 2.5                   | 3                | mA     |                                     |

| Output Quiescent Supply Current                 |                    |                                       | •                     |                  | -      |                                     |

| IL711                                           | т                  |                                       | 5                     | 6                | mA     |                                     |

| IL712                                           | - I <sub>DD2</sub> |                                       | 2.5                   | 3                | mA     |                                     |

| Logic Input Current                             | II                 | -10                                   |                       | 10               | μΑ     |                                     |

| Logic High Output Voltage                       | V <sub>OH</sub>    | $V_{DD} - 0.1$                        | V <sub>DD</sub>       |                  | v      | $I_O = -20 \ \mu A, \ V_I = V_{IH}$ |

| Logie ingli o uput + onuge                      | · On               | $0.8 \ge V_{DD}$                      | 0.9 x V <sub>DD</sub> |                  | •      | $I_0 = -4 \text{ mA}, V_I = V_{IH}$ |

| Logic Low Output Voltage                        | V <sub>OL</sub>    |                                       | 0                     | 0.1              | v      | $I_O = 20 \ \mu A, \ V_I = V_{IL}$  |

| Logie Low output voluge                         |                    |                                       | 0.5                   | 0.8              | •      | $I_0 = 4 \text{ mA}, V_I = V_{IL}$  |

|                                                 |                    | Switching Spe                         | cifications           |                  | -      |                                     |

| Maximum Data Rate                               |                    |                                       |                       |                  |        |                                     |

| IL711/IL712 and IL711T/IL712T                   |                    | 100                                   | 110                   |                  | Mbps   | $C_L = 15 \text{ pF}$               |

| IL711S and IL712S                               |                    | 130                                   | 150                   |                  | Mbps   | $C_L = 15 \text{ pF}$               |

| Pulse Width <sup>(7)</sup>                      | PW                 | 10                                    | 7.5                   |                  | ns     | 50% Points, Vo                      |

| Propagation Delay Input to Output               | t <sub>PHL</sub>   |                                       | 10                    | 15               | ns     | $C_{L} = 15 \text{ pF}$             |

| (High to Low)                                   | THE                |                                       |                       |                  |        |                                     |

| Propagation Delay Input to Output               | t <sub>PLH</sub>   |                                       | 10                    | 15               | ns     | $C_{L} = 15 \text{ pF}$             |

| (Low to High)                                   | 1.2.11             |                                       |                       |                  |        |                                     |

| Pulse Width Distortion <sup>(2)</sup>           |                    |                                       |                       |                  |        |                                     |

| IL711/IL712 and IL711T/IL712T                   | PWD                |                                       | 2                     | 3                | ns     | $C_L = 15 \text{ pF}$               |

| IL711S and IL712S                               |                    |                                       | 0.3                   | 3                |        |                                     |

| Propagation Delay Skew <sup>(3)</sup>           | t <sub>PSK</sub>   |                                       | 4                     | 6                | ns     | $C_L = 15 \text{ pF}$               |

| Output Rise Time (10%–90%)                      | t <sub>R</sub>     |                                       | 1                     | 3                | ns     | $C_L = 15 \text{ pF}$               |

| Output Fall Time (10%–90%)                      | t <sub>F</sub>     |                                       | 1                     | 3                | ns     | $C_L = 15 \text{ pF}$               |

| Common Mode Transient Immunity                  | $ CM_H ,  CM_L $   | 20                                    | 30                    |                  | kV/μs  | $V_{cm} = 300 V$                    |

| (Output Logic High or Logic Low) <sup>(4)</sup> |                    |                                       |                       |                  | -      |                                     |

| Channel to Channel Skew                         | t <sub>CSK</sub>   |                                       | 2                     | 3                | ns     | $C_L = 15 \text{ pF}$               |

| Dynamic Power Consumption <sup>(6)</sup>        |                    | · · · · · · · · · · · · · · · · · · · | 200                   | 340              | µA/MHz | per channel                         |

|                                                 | Magnetic Field     |                                       |                       | $V_{DD1} < 5.5V$ |        |                                     |

| Power Frequency Magnetic Immunity               | H <sub>PF</sub>    | 2800                                  | 3500                  |                  | A/m    | 50Hz/60Hz                           |

| Pulse Magnetic Field Immunity                   | H <sub>PM</sub>    | 4000                                  | 4500                  |                  | A/m    | $t_p = 8\mu s$                      |

| Damped Oscillatory Magnetic Field               | H <sub>OSC</sub>   | 4000                                  | 4500                  |                  | A/m    | 0.1Hz – 1MHz                        |

| Cross-axis Immunity Multiplier <sup>(9)</sup>   | K <sub>X</sub>     |                                       | 2.5                   |                  |        |                                     |

#### Notes (apply to both 3.3 V and 5 V specifications):

- 1. Absolute maximum ambient operating temperature means the device will not be damaged if operated under these conditions. It does not guarantee performance.

- 2. PWD is defined as  $|t_{PHL} t_{PLH}|$ . %PWD is equal to PWD divided by pulse width.

- 3.  $t_{PSK}$  is the magnitude of the worst-case difference in  $t_{PHL}$  and/or  $t_{PLH}$  between devices at 25°C.

- 4.  $CM_{H}$  is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 > 0.8 V_{DD2}$ .  $CM_L$  is the maximum common mode input voltage that can be sustained while maintaining  $V_0 < 0.8 V$ . The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

- 5. Device is considered a two terminal device: pins 1–4 shorted and pins 5–8 shorted.

- 6. Dynamic power consumption is calculated per channel and is supplied by the channel's input side power supply.

- 7. Minimum pulse width is the minimum value at which specified PWD is guaranteed.

- 8. The relevant test and measurement methods are given in the Electromagnetic Compatibility section on p. 6.

- 9. External magnetic field immunity is improved by this factor if the field direction is "end-to-end" rather than to "pin-to-pin" (see diagram on p. 6).

# **Application Information**

#### **Electrostatic Discharge Sensitivity**

This product has been tested for electrostatic sensitivity to the limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

#### **Electromagnetic Compatibility**

IL700-Series Isolators are fully compliant with generic EMC standards EN50081, EN50082-1 and the umbrella line-voltage standard for Information Technology Equipment (ITE) EN61000. The IsoLoop Isolator's Wheatstone bridge configuration and differential magnetic field signaling ensure excellent EMC performance against all relevant standards. NVE conducted compliance tests in the categories below:

EN50081-1

Residential, Commercial & Light Industrial Methods EN55022, EN55014

EN50082-2: Industrial Environment

Methods EN61000-4-2 (ESD), EN61000-4-3 (Electromagnetic Field Immunity), EN61000-4-4 (Electrical Transient Immunity), EN61000-4-6 (RFI Immunity), EN61000-4-8 (Power Frequency Magnetic Field Immunity), EN61000-4-9 (Pulsed Magnetic Field), EN61000-4-10 (Damped Oscillatory Magnetic Field) ENV50204

Radiated Field from Digital Telephones (Immunity Test)

Immunity to external magnetic fields is even higher if the field direction is "end-to-end" rather than to "pin-to-pin" as shown in the diagram below:

Cross-axis Field Direction

# **Dynamic Power Consumption**

IsoLoop Isolators achieve their low power consumption from the way they transmit data across the isolation barrier. By detecting the edge transitions of the input logic signal and converting these to narrow current pulses, a magnetic field is created around the GMR Wheatstone bridge. Depending on the direction of the magnetic field, the bridge causes the output comparator to switch following the input logic signal. Since the current pulses are narrow, about 2.5 ns, the power consumption is independent of mark-to-space ratio and solely dependent on frequency. This has obvious advantages over optocouplers, which have power consumption heavily dependent on mark-to-space ratio.

# **Power Supply Decoupling**

Both power supplies to these devices should be decoupled with low-ESR 47 nF ceramic capacitors. Ground planes for both  $GND_1$ and  $GND_2$  are highly recommended for data rates above 10 Mbps. Capacitors must be located as close as possible to the V<sub>DD</sub> pins.

# Signal Status on Start-up and Shut Down

To minimize power dissipation, input signals are differentiated and then latched on the output side of the isolation barrier to reconstruct the signal. This could result in an ambiguous output state depending on power up, shutdown and power loss sequencing. Therefore, the designer should consider including an initialization signal in the start-up circuit. Initialization consists of toggling the input either high then low, or low then high.

# **Data Transmission Rates**

The reliability of a transmission system is directly related to the accuracy and quality of the transmitted digital information. For a digital system, those parameters which determine the limits of the data transmission are pulse width distortion and propagation delay skew.

Propagation delay is the time taken for the signal to travel through the device. This is usually different when sending a low-to-high than when sending a high-to-low signal. This difference, or error, is called pulse width distortion (PWD) and is usually in nanoseconds. It may also be expressed as a percentage:

$PWD\% = \frac{Maximum Pulse Width Distortion (ns)}{Signal Pulse Width (ns)} \times 100\%$

For example, with data rates of 12.5 Mbps:

$$PWD\% = \frac{3 \text{ ns}}{80 \text{ ns}} \times 100\% = 3.75\%$$

This figure is almost **three times** better than any available optocoupler with the same temperature range, and **two times** better than any optocoupler regardless of published temperature range. IsoLoop isolators exceed the 10% maximum PWD recommended by PROFIBUS, and will run to nearly 35 Mb within the 10% limit.

Propagation delay skew is the signal propagation difference between two or more channels. This becomes significant in clocked systems because it is undesirable for the clock pulse to arrive before the data has settled. Short propagation delay skew is therefore especially critical in high data rate parallel systems for establishing and maintaining accuracy and repeatability. Worstcase channel-to-channel skew in an IL700 Isolator is only 3 ns, which is **ten times** better than any optocoupler. IL700 Isolators have a maximum propagation delay skew of 6 ns, which is **five times** better than any optocoupler.

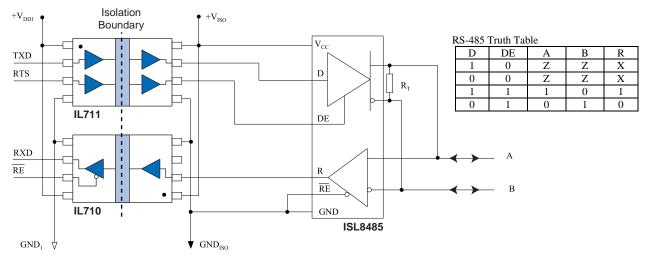

## **Application Diagrams**

#### **Isolated PROFIBUS / RS-485**

NVE offers a unique line of PROFIBUS / RS-485 transceivers, but IL700 high-speed digital signal isolators can also be used as part of multi-chip designs with non-isolated PROFIBUS transceivers.

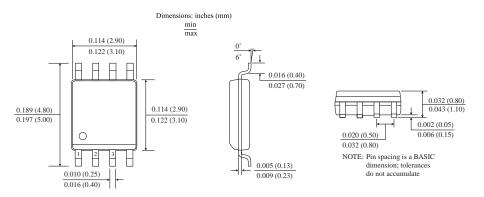

## Package Drawings, Dimensions and Specifications

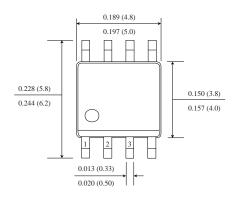

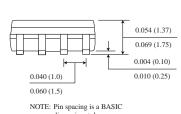

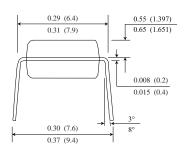

#### 8-pin MSOP

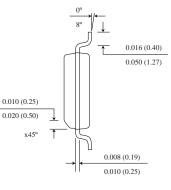

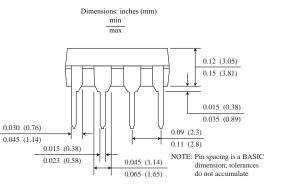

# 8-pin SOIC Package

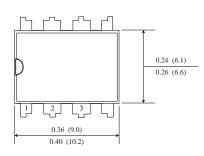

Dimensions in inches (mm)

dimension; tolerances do not accumulate

## 8-pin PDIP

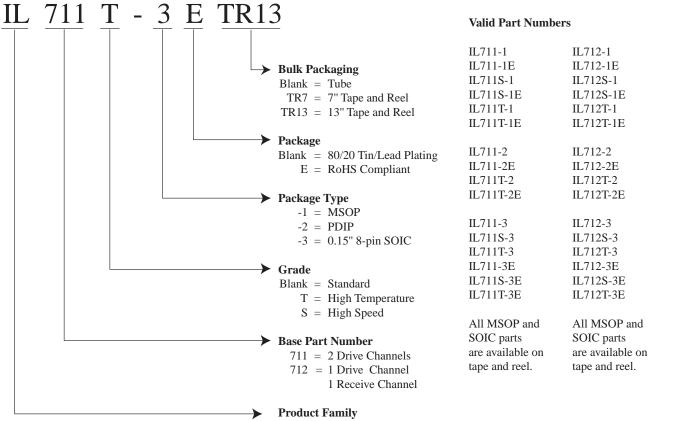

#### Ordering Information and Valid Part Numbers

IL = Isolators

| ISB-DS-001-IL711/12-Q<br>March 2008 | <ul> <li>Changes</li> <li>Added magnetic field immunity and electromagnetic compatibility specifications.</li> </ul>                                                              |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISB-DS-001-IL711/12-P               | <ul><li>Changes</li><li>Correct SOIC package drawing.</li></ul>                                                                                                                   |

| ISB-DS-001-IL711/12-O               | <ul> <li>Changes</li> <li>Note on all package drawings that pin-spacing tolerances are non-accumulating; change MSOP pin-spacing dimensions and tolerance accordingly.</li> </ul> |

| ISB-DS-001-IL711/12-N               | <ul><li>Changes</li><li>Changed lower limit of length on PDIP package drawing.</li></ul>                                                                                          |

|                                     | • Tightened pin-spacing tolerance on MSOP package drawing.                                                                                                                        |

| ISB-DS-001-IL711/12-M               | <ul> <li>Changes</li> <li>Changed ordering information to reflect that devices are now fully RoHS compliant with no exemptions.</li> </ul>                                        |

| ISB-DS-001-IL711/12-L               | <ul><li>Changes</li><li>Eliminated soldering profile chart</li></ul>                                                                                                              |

| ISB-DS-001-IL711/12-K               | <ul> <li>Changes</li> <li>Added RS-485 application circuit</li> </ul>                                                                                                             |

| ISB-DS-001-IL711/12-J               | <ul> <li>Changes</li> <li>MSOP packages, S- and T-Grades added</li> <li>Order information updated</li> </ul>                                                                      |

| ISB-DS-001-IL711/12-I               | Changes                                                                                                                                                                           |

|                                     | Added MSOP Specifications                                                                                                                                                         |

|                                     | Updated IEC and UL Approval Numbers                                                                                                                                               |

# About NVE

An ISO 9001 Certified Company

NVE Corporation manufactures innovative products based on unique spintronic Giant Magnetoresistive (GMR) technology. Products include Magnetic Field Sensors, Magnetic Field Gradient Sensors (Gradiometers), Digital Magnetic Field Sensors, Digital Signal Isolators, and Isolated Bus Transceivers.

NVE pioneered spintronics and in 1994 introduced the world's first products using GMR material, a line of ultra-precise magnetic sensors for position, magnetic media, gear speed and current sensing.

NVE Corporation 11409 Valley View Road Eden Prairie, MN 55344-3617 USA Telephone: (952) 829-9217 Fax: (952) 829-9189 Internet: www.nve.com e-mail: <u>isoinfo@nve.com</u>

The information provided by NVE Corporation is believed to be accurate. However, no responsibility is assumed by NVE Corporation for its use, nor for any infringement of patents, nor rights or licenses granted to third parties, which may result from its use. No license is granted by implication, or otherwise, under any patent or patent rights of NVE Corporation. NVE Corporation does not authorize, nor warrant, any NVE Corporation product for use in life support devices or systems or other critical applications, without the express written approval of the President of NVE Corporation.

Specifications shown are subject to change without notice.

ISB-DS-001-IL711/12-Q March 2008